Alle Kategorien

-

Integrierte schaltkreise (ICS)

Integrierte schaltkreise (ICS)

- Schnittstelle - Sensor, kapazitive Berührung(642)

- Spezialisierte ICS(12302)

- PMIC-Spannungsregler-besonderer Zweck(5644)

- PMIC-Spannungsregler-lineare Regler(793)

- PMIC-Spannungsregler-linear + Switching(1829)

- PMIC-Spannungsregler-linear(70981)

- PMIC-Spannungsregler-DC DC Switching Regulators(39569)

- PMIC-Regler-DC-DC-Switching-Controller(13507)

- PMIC-Spannungs-Referenz(9453)

- PMIC-v/f und f/v-Wandler(145)

- PMIC-Thermal Management(592)

- PMIC-Supervisor(47946)

- PMIC-RMS bis DC-Wandler(170)

- PMIC-Netzteil-Controller, Monitore(2104)

- PMIC-Power over Ethernet (PoE) Controller(1008)

- PMIC-Power Management-spezialisierte(7722)

- PMIC-Netzschalter, Treiber laden(7706)

- PMIC-PFC (Power Factor Correction)(1222)

- PMIC oder Steuerungen, ideale Dioden(705)

- PMIC-Motor-Treiber, Regler(4712)

- PMIC-Beleuchtung, Ballast-Regler(560)

- PMIC-LED-Treiber(7282)

- PMIC-Laser-Treiber(573)

- PMIC-Hot-Swap-Controller(2816)

- PMIC-Gate-Treiber(7083)

- PMIC-voll, Half-Bridge-Treiber(1342)

- PMIC-Energy Messung(654)

- PMIC-Display-Treiber(1435)

- PMIC-derzeitige Regulierung/Management(1481)

- PMIC-Batterie-Management(5553)

- PMIC-Ladegeräte(3831)

- PMIC-AC DC Konverter, Offline Schalter(4905)

- Memory-Controller(358)

- Memory-Konfigurations-Proms für FPGAs(639)

- Speicher-Akkus(13)

- Erinnerung(65694)

- Logic-universelle Bus-Funktionen(706)

- Logic-Übersetzer, Level-Shifter(2854)

- Logik-Specialty Logic(1870)

- Logik-Signal-Schalter, Multiplexer, Decoder(9420)

- Logic-Shift-Register(2665)

- Logic-Parity Generatoren und Checkers(335)

- Logic-multivibratoren(831)

- Logik-Latches(3658)

- Logik - Tore und Wechselrichter - Multifunktion, konfigurierbar(1687)

- Logik-Tore und Wechselrichter(16453)

- Logic-Flip Flops(7780)

- Logik-FIFOs Speicher(4240)

- Logik-Zähler, Trennlinien(3456)

- Logik-Vergleichsoperator(592)

- Logik-Puffer, Treiber, Receiver, Transceiver(17835)

- Linear-Video-Verarbeitung(2909)

- Linear-Vergleichsoperator(5084)

- Linear-analoge Multiplikatoren, Trennwände(263)

- Linear-Verstärker-Video Amps und Module(1905)

- Linear-Verstärker-Spezial-Zweck(1856)

- Linear - Verstärker - Instrumentierung, OP -Verstärker, Pufferverstärker(34236)

- Linear-Verstärker-Audio(4567)

- Interface-Voice Record und Playback(556)

- Schnittstelle - UARTs (Universal Asynchronous Receivers -Sender)(1236)

- Schnittstelle-Telecom(4467)

- Interface-spezialisierte(4833)

- Interface-Signal Terminatoren(333)

- Interface-Signal-Puffer, Repeater, Splitter(1449)

- Interface-Serializer, Deserializer(1480)

- Schnittstellen-Sensor und Detektor-Interfaces(1524)

- Interface-Module(169)

- Interface-Modems-ICS und Module(407)

- Interface-e/a-Expander(1136)

- Interface-Filter-aktiv(1226)

- Interface-Encoder, Decoder, Konverter(714)

- Interface-Treiber, Receiver, Transceiver(20755)

- Interface-Direct Digital Synthesis (DDS)(117)

- Interface-Controller(3628)

- Interface-Codecs(1676)

- Schnittstelle - Analoge Switches, Multiplexer, Demultiplexer(12567)

- Schnittstelle-analoge Schalter-spezieller Zweck(2533)

- Embedded-System on Chip (SoC)(4496)

- Embedded-PLDs (programmierbare Logik-Vorrichtung)(971)

- Embedded-Mikroprozessoren(10083)

- Embedded-Mikrocontroller-anwendungsspezifische(2275)

- Embedded-Mikrocontroller(99285)

- Eingebettet - Mikrocontroller, Mikroprozessor, FPGA -Module(1527)

- Eingebettet - FPGAs (Feldprogrammiergate -Array) mit Mikrocontrollern(81)

- Embedded-FPGAs (Field Programmable Gate Array)(27748)

- Embedded-DSP (Digital Signal Processors)(4081)

- Eingebettet - CPLDs (komplexe programmierbare Logikgeräte)(5187)

- Datenerfassung-Touch Screen Controller(1210)

- Datenerfassung-Digital to Analog Converter (DAC)(14419)

- Datenerfassung-digitale Potentiometer(6250)

- Datenerfassung-analog zu Digital Converters (ADC)(17776)

- Datenerfassung-analoges Frontend (AFE)(787)

- Datenerfassung-MDE/DACs-spezieller Zweck(3043)

- Clock/Timing-Uhren in Echtzeit(2446)

- Uhr/Timing - programmierbare Timer und Oszillatoren(23469)

- Clock/Timing-IC-Akkus(4)

- Takt/Timing-Delay Lines(1049)

- Uhr/Timing - Uhrengeneratoren, PLLS, Frequenzsynthesizer(32775)

- Clock/Timing-Clock Puffer, Treiber(4568)

- Clock/Timing-anwendungsspezifische(8652)

- Audio Spezial-Zweck(1564)

-

Diskrete Halbleiter-Produkte

Diskrete Halbleiter-Produkte

- Aktuelle Regulierung - Dioden, Transistoren(1090)

- Transistoren-besonderer Zweck(226)

- Transistoren-programmierbare Unijunction(48)

- Transistoren-jfets(1558)

- Transistoren-IGBTs-Einzel(4799)

- Transistoren-IGBTs-Module(63420)

- Transistoren-IGBTs-Arrays(26)

- Transistoren-FETs, MOSFETs-Einzel(48330)

- Transistoren-FETs, MOSFETs-RF(4903)

- Transistoren-FETs, MOSFETs-Arrays(6641)

- Transistoren-Bipolar (BJT)-einzeln, Pre-biased(4539)

- Transistoren-Bipolar (BJT)-Einzel(25800)

- Transistoren-Bipolar (BJT)-RF(2087)

- Transistoren-bipolare (BJT)-Arrays, Pre-biased(2115)

- Transistoren-bipolare (BJT)-Arrays(2310)

- Thyristor-triacs(4044)

- Thyristoren-SCRs-Module(3967)

- Thyristoren-SCRs(5436)

- Thyristoren-diacs, sidacs(319)

- Power Driver Module(1627)

- Dioden-zenerdioden-Einzel(87483)

- Dioden-zenerdioden-Arrays(2619)

- Dioden - variable Kapazität (Varik, Varaktoren)(1200)

- Dioden-RF(2753)

- Dioden-Gleichrichter-Einzel(67528)

- Dioden-Gleichrichter-Arrays(20581)

- Dioden-Brücke-Gleichrichter(11700)

-

RF/if und RFID

RF/if und RFID

- SIM -Karten für Abonnenten -Identifikationsmodul (SIM)(77)

- RF -Zirkulatoren und Isolatoren(1742)

- RFID, RF-Zugang, Monitoring-ICS(1550)

- RFID Transponder, Tags(747)

- RFID Lesegeräte(464)

- RFID -Bewertungs- und Entwicklungskits, Boards(30)

- RFID Antennen(329)

- RFI und EMI - Abschirm- und Absorbungsmaterialien(6444)

- HF und EMI-Kontakte, Fingerstock und Dichtungen(7497)

- RF Transmitter(668)

- RF Transceiver Module(6900)

- RF-Transceiver ICS(4169)

- HF-Schalter(9276)

- RF Shields(16401)

- HF-Receiver(1998)

- HF -Empfänger, Sender und Transceiver -Einheiten(2763)

- RF Power Divider/Splitter(1223)

- RF Power Controller ICs(86)

- HF-Modulatoren(710)

- HF-Mixer(2800)

- RF misc ICS und Module(3276)

- HF-Front-End (LNA + PA)(419)

- RF -Bewertungs- und Entwicklungskits, Boards(747)

- HF-gerichtete Kupplung(2718)

- RF Diplexer(1464)

- RF-Detektoren(412)

- RF-Demodulatoren(249)

- HF-Antennen(12319)

- HF-Verstärker(19651)

- Balun(1496)

- Dämpfungsglieder(4852)

-

Optoelektronik

Optoelektronik

- Optomechanisch(480)

- Leuchten(125)

- Laserdioden, Lasermodule - Laserlieferung, Laserfasern(345)

- Hene Lasersysteme(31)

- Hene Laserköpfe(27)

- Hintergrundbeleuchtung anzeigen(93)

- Xenon-Beleuchtung(387)

- Touchscreen-Overlays(453)

- Panel Indicators, Pilot Lights(75729)

- Optik-Remote-Phosphor-Lichtquelle(269)

- Optik-Reflektoren(665)

- Optik-leichte Rohre(5384)

- Optik-Objektive(4951)

- LEDs-Spacer, Unentschieden(2718)

- LEDs-Lamp-Ersetzungen(29718)

- LEDs - Leiterplattenindikatoren, Arrays, Lichtstäbe, Balkendiagramme(9083)

- LED-thermische Produkte(667)

- LED-Beleuchtung(64)

- LED-Beleuchtung-weiß(37580)

- LED-Beleuchtung-Farbe(4728)

- LED-Beleuchtung-Maiskolben, Motoren, Module(28735)

- LED-Anzeige-diskret(27601)

- Laserdioden, Module(1553)

- Lampen-Glühlampen, Neons(311004)

- Lampen-Kälte-Fluoreszenz (KKL) & UV(164)

- Wechselrichter(7728)

- Infrarot, UV, sichtbare Strahler(3871)

- Fiber Optics-Transmitter-Antrieb integriert(4085)

- Fiber Optics-Transmitter-diskrete(350)

- Fiber Optics-Transceiver Module(18758)

- Fiberoptik-Switches, Multiplexer, Demultiplexer(1387)

- Fiberoptik-Receiver(695)

- Fiberoptik-Dämpfung(654)

- Elektrolumineszenz(102)

- Display, Monitor-Interface Controller(98)

- Display-Module-Vakuum-Leuchtstofflampen (VFD)(249)

- Module anzeigen-LED Dot Matrix und Cluster(865)

- Display-Module-LED-Zeichen und numerische(5421)

- Display-Module-LCD, OLED, Graphic(4654)

- Display-Module-LCD, OLED-Zeichen und numerische(2202)

- Display-Blenden, Objektive(88)

- Adresse, Spezialität(458)

-

Sensoren, Wandler

Sensoren, Wandler

- Ultraschallempfänger, Sender - Industrial(115)

- Temperatursensoren - Thermostate - Mechanisch - Industrielles(3103)

- Temperatursensoren - Analog und digitaler Ausgang - Industrial(209)

- Näherungssensoren - Industrial(13611)

- Drucksensoren, Wandler - Industrie(26503)

- Optische Sensoren - Photonik - Zähler, Detektoren, SPCM (Einzelphotonzählmodul)(751)

- Optische Sensoren - Kameramodule(875)

- Magnetsensoren - Position, Nähe, Geschwindigkeit (Module) - Industrie(554)

- Kraftsensoren - Industrial(346)

- Flusssensoren - Industrielles(151)

- Float, Level Sensoren - Industrial(310)

- Encoder - Industrial(4980)

- Farbsensoren - Industrial(50)

- Berührungssensoren(100)

- Ultraschall-Receiver, Transmitter(2421)

- Temperatursensoren-Thermostat-Solid State(1096)

- Temperatursensoren-Thermostate-mechanisch(3397)

- Temperatursensoren - Thermoelemente, Temperatursonden(1921)

- Temperatursensoren - RTD (Widerstandstemperaturdetektor)(1525)

- Temperatursensoren-PTC-Thermistoren(2273)

- Temperatursensoren-ntc-thermistoren(13259)

- Temperatursensoren-Analog und Digital Output(3928)

- DMS(1399)

- Spezialisierte Sensoren(1861)

- Solarzellen(503)

- Schock-Sensoren(84)

- Sensor-Interface-Junction-Blöcke(2519)

- Sensor-Kabel-Baugruppen(22011)

- Proximity/Belegung Sensoren-fertige Einheiten(725)

- Näherungsschalter(2860)

- Drucksensoren, Wandler(11317)

- Positionssensoren - Winkel, lineare Positionsmessung(6022)

- Optische Sensoren-reflektierende-Logik-Ausgang(194)

- Optische Sensoren - reflektierend - analoge Ausgang(432)

- Optische Sensoren-Phototransistoren(1027)

- Optische Sensoren - Photointerrupter - Schlitztyp - Transistorausgang(1427)

- Optische Sensoren - Photointerrupter - Schlitztyp - Logikausgabe(1215)

- Optische Sensoren-Lichtschranke, Industrial(16763)

- Optische Sensoren-Photodioden(1543)

- Optische Sensoren-Foto-Detektoren-Remote Receiver(2605)

- Optische Sensoren-Foto-Detektoren-Logik-Ausgang(146)

- Optische Sensoren-Foto-Detektoren-CDs-Zellen(74)

- Optische Sensoren-Distanz-Messung(377)

- Optische Sensoren-Ambient Light, IR, UV Sensoren(1305)

- Multifunktions(558)

- Motion Sensors-Vibration(337)

- Motion Sensors-Tilt Schalter(67)

- Bewegungsmelder-optisch(719)

- Motion Sensors-Neigungssensoren(175)

- Motion Sensors-Imus (Trägheit-Maßeinheiten)(416)

- Motion Sensors-Kreisel(214)

- Motion Sensors-Beschleunigungsmesser(1911)

- Magnete-Sensor abgestimmt(119)

- Magnete-Multi Purpose(1965)

- Magnetische Sensoren-Schalter (Solid State)(3700)

- Magnetsensoren - Position, Nähe, Geschwindigkeit (Module)(5199)

- Magnetische Sensoren-linear, Kompass (ICS)(1247)

- Magnetsensoren - Kompass, Magnetfeld (Module)(35)

- LVDT -Wandler (linearer variabler Differentialtransformator)(204)

- IrDA Transceiver-Module(196)

- Bildsensor, Kamera(2235)

- Feuchtigkeit-Sensoren(1425)

- Gas-Sensoren(1217)

- Force Sensoren(188)

- Durchfluss-Sensoren(550)

- Float, Level Sensoren(1343)

- Encoder(6357)

- Staub-Sensoren(43)

- Aktuelle Wandler(3455)

- Color Sensoren(85)

- Verstärker(1905)

-

Anschlüsse, Verbindungen

Anschlüsse, Verbindungen

- USB, DVI, HDMI -Stecker(446)

- Festkörperbeleuchtungsstecker(555)

- Steckdosen für ICs, Transistoren(953)

- Steckbare Steckverbinder(1221)

- Photovoltaik (Solarpanel) Anschlüsse(136)

- Glasfaseranschlüsse(370)

- FFC, FPC (flache flexible) Anschlüsse(761)

- D-Sub, D-förmige Stecker(2887)

- Koaxialverbinder (RF)(2389)

- Rundanschlüsse(14162)

- Stromanbeter Blade Type(273)

- Stecker und Behälter(2597)

- USB, DVI, HDMI Stecker-Adapter(572)

- USB, DVI, HDMI -Stecker(4298)

- Klemmen-Wire to Board Steckverbinder(217)

- Klemmen-Draht-Steckverbinder(4322)

- Klemmen-Draht-Pin Stecker(328)

- Terminals-Revolver Steckverbinder(1273)

- Terminals-spezialisierte Steckverbinder(2042)

- Klemmen-Spaten Verbinder(3902)

- Klemmen-Löten/Stecker(345)

- Klemmen-Verschraubungen(745)

- Klemmen-Ring Steckverbinder(12596)

- Klemmen-rechteckige Steckverbinder(4747)

- Terminals - Schnellverbindungen, schnelle Trennungsanschlüsse(8514)

- Klemmen-PC PIN, Single Post Connectors(3776)

- Klemmen-PC-Pin-Buchsen, Sockel-Steckverbinder(5883)

- Klemmen-magnetische Draht-Steckverbinder(1653)

- Klemmen-Messer Steckverbinder(112)

- Klemmen-Gehäuse, Stiefel(2850)

- Klemmen-Folie Steckverbinder(108)

- Klemmen-Barrel, Bullet-Steckverbinder(1107)

- Klemmen-Adapter(137)

- Terminal-Streifen und Revolver-Boards(1159)

- Terminal Junction Systeme(2533)

- Anschlussblöcke-Draht an Bord(43615)

- Terminal Blocks-spezialisierte(3722)

- Terminal Blocks-Power Distribution(847)

- Anschlussblöcke-Panel Mount(1359)

- Terminal Blocks-Interface Module(1819)

- Anschlussblöcke-Kopfzeilen, Stecker und Buchsen(119920)

- Anschlussblöcke-DIN-Schiene, Kanal(9373)

- Anschlussblöcke-Kontakte(65)

- Anschlussblöcke-Barrier Blocks(47517)

- Anschlussblöcke-Adapter(1059)

- Solid State Lighting Verbinder-Kontakte(271)

- Festkörperbeleuchtungsstecker(1344)

- Buchsen für ICS, Transistoren-Adapter(275)

- Steckdosen für ICs, Transistoren(22148)

- Shunts, Jumper(907)

- Rechteckige Verbinder-Feder geladen(7721)

- Rechteckige Steckverbinder-Gehäuse(43023)

- Rechteckige Verbinder-Kopfzeilen, Spezial-PIN(6129)

- Rechteckige Anschlüsse - Header, Gefäße, weibliche Sockel(229601)

- Rechteckige Verbinder-Kopfzeilen, männliche Pins(543338)

- Rechteckige Anschlüsse - kostenloses Hängen, Panelhalterung(30142)

- Rechteckige Verbinder-Kontakte(10681)

- Rechteckige Anschlüsse - Board in, Direktdraht zum Board(2432)

- Rechteckige Verbinder-Adapter(475)

- Rechteckig - Brett zu Board -Steckern - Header, Behälter, weibliche Sockel(9)

- Rechteckig - Brett zu Board -Steckern - Header, männliche Stifte(2)

- Rechteckige Anschlüsse - Board -Abstandshalter, Stacker (Board zu Board)(238901)

- Rechteckige Anschlüsse - Arrays, Kantentyp, Mezzanin (Board zu Board)(37853)

- Stromanschluss-Eingänge, Steckdosen, Module(10310)

- Steckbare Steckverbinder(6049)

- Photovoltaik- (Solarpanel) Anschlüsse - Kontakte(77)

- Photovoltaik (Solarpanel) Anschlüsse(504)

- Modulare Steckverbinder-Verdrahtung Blöcke(99)

- Modulare Steckverbinder-Stecker(1674)

- Modulare Steckverbinder-Stecker Gehäuse(181)

- Modulare Steckverbinder-Buchsen mit magnetischen(10152)

- Modulare Steckverbinder-Buchsen(23416)

- Modulare Steckverbinder-Adapter(855)

- Memory Connectors-PC Cards-Adapter(21)

- Memory Connectors-PC Card Sockets(3299)

- Memory Connectors-Inline Modul Sockets(3390)

- LGH Steckverbinder(764)

- Keystone-Einsätze(2758)

- Keystone-Frontplatte, Frames(1926)

- Heavy Duty Steckverbinder-Einsätze, Module(4190)

- Schwerlastanschlüsse - Gehäuse, Kapuzen, Basen(17226)

- Heavy Duty Steckverbinder-Frames(523)

- Heavy Duty Steckverbinder-Kontakte(1832)

- Heavy Duty Steckverbinder-Baugruppen(671)

- LWL-Steckverbinder-Gehäuse(919)

- Glasfaser-Steckverbinder - Adapter(4455)

- LWL-Steckverbinder(3001)

- FFC, FPC (flache flexible) Steckverbinder - Gehäuse(652)

- FFC, FPC (flache flexible) Anschlüsse - Kontakte(202)

- FFC, FPC (flache flexible) Anschlüsse(18691)

- D-Sub, d-förmige Steckverbinder-Terminatoren(47)

- D-Sub, d-förmige Steckverbinder-Gehäuse(12238)

- D-Sub, d-förmige Steckverbinder-Kontakte(2714)

- D-Sub, D-förmige Steckverbinder-Rückenschalen, Kapuzen(5995)

- D-Sub, d-förmige Steckverbinder-Adapter(1304)

- D-Sub Steckverbinder(141346)

- D-förmige Steckverbinder-Centronics(8770)

- Kontakte, Frühling geladen und Druck(630)

- Kontakte-Multi Purpose(6196)

- Kontakte-"Leadframe"(122)

- Koaxial-Steckverbinder (RF)-Terminatoren(1231)

- Koaxial-Steckverbinder (RF)-Kontakte(480)

- Koaxial-Steckverbinder (RF)-Adapter(6386)

- Koaxialverbinder (RF)(25734)

- Rundsteckverbinder-Gehäuse(441226)

- Rundsteckverbinder-Kontakte(4737)

- Rundsteckverbinder-backschalen und Kabel-Klemmen(53692)

- Rundsteckverbinder-Adapter(8839)

- Rundanschlüsse(1196254)

- Card Edge Steckverbinder-Gehäuse(469)

- Karte Edge Verbinder-edgeboard Verbinder(672683)

- Card Edge Verbinder-Kontakte(325)

- Card Edge Verbinder-Adapter(73)

- Blade Type Power Steckverbinder-Gehäuse(837)

- Blade Type Power Connectors-Kontakte(393)

- Stromanbeter Blade Type(4163)

- Zwischen Serien-Adapter(649)

- Barrel-Stromanschluss(935)

- Barrel-Audio-Anschlüsse(2432)

- Barrel-Audio Adapter(92)

- Banana und Tip Steckverbinder-Buchsen, Stecker(1644)

- Banana and Tip Connectors-Binding Posts(239)

- Banana und Tip Steckverbinder-Adapter(75)

- Backplane Steckverbinder-spezialisiert(45586)

- Backplane Steckverbinder-Gehäuse(6863)

- Backplane Steckverbinder-Hard metrisch, Standard(6297)

- Backplane Steckverbinder-DIN 41612(9408)

- Backplane Steckverbinder-Kontakte(3583)

- Backplane Connectors-ARINC Einsätze(2357)

- Backplane Steckverbinder-ARINC(3789)

-

Widerstände

-

Kondensatoren

Kondensatoren

- Aluminium-Elektrolytkondensatoren(16817)

- Trimmer, Variable Kondensatoren(3151)

- Dünne Folien-Kondensatoren(3473)

- Tantal-Kondensatoren(136103)

- Tantal-Polymer-Kondensatoren(9778)

- Silizium-Kondensatoren(320)

- Niob Oxide Kondensatoren(330)

- Mica und PTFE Kondensatoren(9101)

- Folien-Kondensatoren(150406)

- Elektrische Doppelschichtkondensatoren (EDLC), Superkondensatoren(2782)

- Keramische Kondensatoren(833829)

- Kondensatoren-Netzwerke, Arrays(2383)

- Aluminium-Elektrolytkondensatoren(125325)

- Aluminium-Polymer-Kondensatoren(7544)

-

Transformatoren

-

Isolatoren

-

Kristalle, Oszillatoren, Resonatoren

-

Switches

Switches

- Verriegelungsschalter(2893)

- Emergency-Stop-Schalter (E-Stop)(1160)

- Kabelzugschalter(571)

- Toggle-Schalter(33608)

- Rändelrads Schalter(742)

- Schalter(14263)

- Snap-Aktion, Endschalter begrenzen(28077)

- Slide-Schalter(5166)

- Selector-Schalter(9720)

- Rotary Switches(13850)

- Rocker Schalter(53790)

- Drucktaste-Schalter-Hall-Effekt(127)

- Drucktaste Schalter(190826)

- Programmierbare Display-Switches(39)

- Navigations-Schalter, Joystick(1882)

- Magnetische, Reed-Schalter(1399)

- Keypad-Schalter(637)

- Keylock Schalter(3684)

- DIP Schalter(7747)

- Konfigurierbare Switch-Komponenten-Objektiv(1435)

- Konfigurierbare Schalter-Komponenten-Lichtquelle(1236)

- Konfigurierbare Switch-Komponenten-Contact Block(1401)

- Konfigurierbare Switch-Komponenten-Body(16077)

- Disconnect-Switch-Komponenten(2567)

-

Relais

Relais

- Sicherheitsrelais(1310)

- Reedrelais(1735)

- Hochfrequenz (RF) -Relais(1190)

- Schütze (Festkörper)(686)

- Schütze (elektromechanisch)(11952)

- Kfz-Relais(1881)

- Solid State Relais(10652)

- Signal-Relais, bis zu 2 Ampere(9149)

- Relay-Sockets(2075)

- Power Relays, über 2 Ampere(31604)

- E / A-Relaismodule(712)

- I/o-Relay-Module-Input(2)

- I/o-Relay-Modul-Racks(247)

Sprache auswählen

Aktuelle Sprache

Deutsch

- English

- Deutsch

- Italia

- Français

- 日本語

- 한국의

- русский

- Svenska

- Nederland

- español

- Português

- polski

- Suomi

- Gaeilge

- Slovenská

- Slovenija

- Čeština

- Melayu

- Magyarország

- Hrvatska

- Dansk

- românesc

- Indonesia

- Ελλάδα

- Български език

- Afrikaans

- IsiXhosa

- isiZulu

- lietuvių

- Maori

- Kongeriket

- Монголулс

- O'zbek

- Tiếng Việt

- हिंदी

- اردو

- Kurdî

- Català

- Bosna

- Euskera

- العربية

- فارسی

- Corsa

- Chicheŵa

- עִבְרִית

- Latviešu

- Hausa

- Беларусь

- አማርኛ

- Republika e Shqipërisë

- Eesti Vabariik

- íslenska

- မြန်မာ

- Македонски

- Lëtzebuergesch

- საქართველო

- Cambodia

- Pilipino

- Azərbaycan

- ພາສາລາວ

- বাংলা ভাষার

- پښتو

- malaɡasʲ

- Кыргыз тили

- Ayiti

- Қазақша

- Samoa

- සිංහල

- ภาษาไทย

- Україна

- Kiswahili

- Cрпски

- Galego

- नेपाली

- Sesotho

- Тоҷикӣ

- Türk dili

- ગુજરાતી

- ಕನ್ನಡkannaḍa

- मराठी

IC -Verpackung: RDL im Vergleich zu anderen Technologien

Zeit: 2024/05/28

Durchsuchen: 4,254

Katalog

Abbildung 1: IC -Verpackung

Verständnis der RDL -Technologie (Umverteilung Schicht)

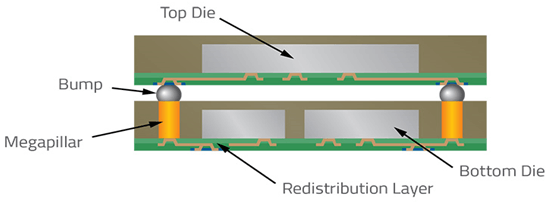

Die RDL -Technologie (Umverteilungsschicht) bedeutet einen erheblichen Fortschritt in der IC -Verpackung (IC).Durch die Einbeziehung einer gemusterten Metallschicht in einen Mikrochip wird die RDL -Technologie ihre elektrischen Verbindungen neu ausrichtet und optimiert.Diese Innovation ermöglicht es in einem einzelnen, effizienteren Paket integriert werden, indem die Eingangs-/Ausgangsanschlüsse (E/O) an die Kanten des Stempels verschoben werden, wodurch die SMT -Verbindungen (Standard -Oberflächenmontage -Technologie) zu einer gedruckten Leiterplatte (PCB (PCB) erleichtert werden kann (PCB).Dieser strategische Umzug ermöglicht eine kompakte Anordnung der Stanze, die den Gesamtabdruck elektronischer Geräte effektiv reduziert.Im Bereich der modernen Elektronik, wo die Raumwirkungsgrad hoch geschätzt wird, bietet die Minimierung der Gerätegröße ohne Kompromisse einen erheblichen Vorteil.

Darüber hinaus handelt es sich bei der RDL -Technologie mehr als nur um Sparen. Die moderne Elektronikbedarf von Hochgeschwindigkeitsleistung und Effizienz, und die RDL-Technologie spielt eine wichtige Rolle bei der Erfüllung dieser Anforderungen. Durch systematisch neuverteilung E/A -Verbindungen reduziert RDL die Signalstörungen und verbessert die elektrische Leistung des Geräts. Dies ist besonders wichtig für Anwendungen, die eine Hochgeschwindigkeitsdatenübertragung und eine präzise Signalintegrität erfordern, z. B. Kommunikationsgeräte, fortschrittliches Computing und Hochfrequenzhandelssysteme. Infolgedessen hilft die RDL -Technologie nicht nur, kleinere Geräte zu schaffen, sondern verbessert auch die elektronische Leistung erheblich.

Abbildung 2: Umverteilung Schicht (RDL) auf Chip

Die Implementierung der RDL -Technologie auf Chips hat die Herstellung elektronischer Geräte revolutioniert, was zur Herstellung von kompakten, aber hoch entwickelten modernen Elektronik führt.Die RDL-Technologie wird ausgiebig bei der Verpackung von MEMS-Geräten (MIMRO-Elektro-Elektro-mechanischen Systemen), Sensoren, Leistungsgeräten, Speichereinheiten, Mikroprozessoren und Grafikprozessoren eingesetzt.Seine Vielseitigkeit macht es zu einem wichtigen Werkzeug für elektronische Gerätedesigner und Hersteller.

Im Zusammenhang mit MEMS -Geräten und -sensoren erleichtert die RDL -Technologie die Erstellung hochkarätiger und effizienter Pakete.Diese Geräte erfordern präzise und zuverlässige Verbindungen, um korrekt zu funktionieren.RDL erreicht dies, indem sie die E/A -Verbindungen zu optimalen Orten umverteilt und eine nahtlose Integration in größere elektronische Systeme gewährleistet.Dies ist besonders relevant für Anwendungen in Automobilelektronik, Medizinprodukten und Unterhaltungselektronik, bei denen sowohl Raumeffizienz als auch hohe Leistung hoch geschätzt werden.

Die RDL -Technologie ist auch der Schlüssel für Verpackungsstärke und Speichereinheiten.Stromversorgungsgeräte, die die elektrische Leistung in elektronischen Systemen verwalten und steuern, profitieren von der verbesserten Konnektivität von RDL, was zu einer verbesserten Leistung und Zuverlässigkeit bei Stromverwaltungsanwendungen führt.In ähnlicher Weise stützen sich Speichereinheiten, die für das Speichern und Abrufen von Daten in elektronischen Geräten verantwortlich sind, auf RDL für einen schnellen und zuverlässigen Datenzugriff.Durch die Optimierung von E/A -Verbindungen verbessert RDL die Gesamtleistung von Speichereinheiten und macht sie effizienter und effektiver.

In Mikroprozessoren und Grafikprozessoren fördert die RDL -Technologie ihre Fähigkeiten erheblich.Mikroprozessoren, die zentralen Verarbeitungseinheiten elektronischer Geräte, erfordern Hochgeschwindigkeitsdatenverarbeitung und effiziente Konnektivität.RDL erreicht dies, indem sie E/A -Verbindungen neu verteilen, die Signalinterferenz reduzieren und die Datenübertragungsgeschwindigkeiten verbessern.Grafikprozessoren, die Renderbilder und -videos verarbeiten, profitieren auch von der verbesserten Konnektivität von RDL, was zu einer schnelleren und effizienteren grafischen Darstellung führt.Dies ist besonders nützlich für Anwendungen in Gaming, virtueller Realität und professioneller Grafik.

Die praktische Anwendung der RDL -Technologie beinhaltet mehrere detaillierte Schritte.Zunächst wird eine dielektrische Schicht am Wafer abgelagert, gefolgt von der Anwendung einer Samenschicht.Die Photolithographie wird dann verwendet, um die Samenschicht zu prüfen und eine Vorlage für die Metallschicht zu erzeugen.Die Elektroplatte wird verwendet, um das Metall abzuscheiden und die RDL zu bilden.Nach der Metallabscheidung wird die überschüssige Samenschicht durch Ätzen entfernt und hinterlässt eine saubere, gemusterte Metallschicht.Schließlich werden Passivierungsschichten hinzugefügt, um die RDL zu schützen und ihre Haltbarkeit zu gewährleisten.

Rolle der Umverteilung der Schichttechnologie

Die Umverteilung der Umverteilung (RDL) erweitert und verbindet die XY -Ebene in Chip -Design und -herstellung, wodurch die Eingangs-/Ausgangsanschlüsse (E/A) von integrierten Schaltungen (ICs) neu konfiguriert werden, um ihr Layout und ihre Funktionalität zu optimieren.Diese Technologie verbessert die Chipverpackungstechniken und erleichtert die Integration mehrerer Chips in ein einzelnes Paket.Auf diese Weise reduziert die RDL -Technologie die Gesamtgröße elektronischer Geräte und hält gleichzeitig hohe Leistung und Zuverlässigkeit.Ingenieure und Designer verwenden RDL, um die Verbindungen innerhalb des Chips zu optimieren und effiziente Funktionen zu gewährleisten, selbst wenn die Geräte kompakter werden.

Verteilern Sie die E/A -Verbindung neu

E/A -Pads, bei denen es sich um Chip -Pin -Verarbeitungsmodule handelt, befinden sich in der Regel am Rand oder an der Peripherie des Chips.Diese Pads verwalten die Signale der Chipstifte, verarbeiten und geben sie dann aus.Die Umverteilungsschicht ermöglicht den Verlagerung dieser E/A -Verbindungen vom Chip in das Paket.Durch das Verbinden der Bond -Pads am Chip mit den Packungsleitungen oder Bällen vereinfacht RDL den Montageprozess und verbessert die Leistung des IC.Während der herkömmliche Anleihedrahtprozess von diesem Setup profitiert, sind Flip-Chip-Anwendungen es schwierig.Hier wird RDL besonders vorteilhaft.Es legt eine Metallschicht zusammen mit einer entsprechenden dielektrischen Schicht auf der Oberfläche des Chips ab und bildet Metalldrähte.Dieser Vorgang überarbeitet die E/A -Anschlüsse in einen neuen, geräumigeren Bereich und erzeugt ein Oberflächenarray -Layout.Diese Anordnung ermöglicht eine effizientere Raumnutzung und eine verbesserte Signalübertragung, wobei die Einschränkungen herkömmlicher Verbindungsmethoden behandelt werden.Techniker, die mit RDL arbeiten, müssen die Ablagerungs- und Strukturierungsprozesse sorgfältig steuern, um eine genaue Ausrichtung und Konnektivität zu gewährleisten.

Routensignale und Kraft

Die Umverteilung Schicht (RDL) ist eine hochrelevante Technologie zum Routing von Signalen und Strom in integrierte Schaltkreise (ICs).Da ICs mit zunehmenden E/A -Verbindungen komplexer geworden sind, ist die Rolle von RDLs deutlicher geworden.Sie werden jetzt häufig in Anwendungen wie Mikroprozessoren, Speicherchips und Sensoren verwendet.Die Fähigkeit der RDL -Technologie, erweiterte Signal- und Leistungsrouting -Anforderungen zu erfüllen, macht es zu einer integralen Komponente in der modernen Elektronik.Die RDL-Technologie unterstützt das Routing von Hochfrequenzsignalen und Stromversorgungen innerhalb des IC, verbessert die Gesamtleistung und die Verringerung der Störungen.Diese Fähigkeit ist besonders vorteilhaft bei Anwendungen, die eine Hochgeschwindigkeitsdatenübertragung und eine präzise Signalintegrität erfordern.Die Verwendung von RDLs hilft bei der Aufrechterhaltung der Signalintegrität durch Minimierung von Überquellen und anderen Formen des Signalabbaues.Ingenieure verwenden fortschrittliche Simulationswerkzeuge, um RDL -Layouts zu entwerfen, die Signalwege und Leistungsverteilung optimieren und die höchsten Leistung und Zuverlässigkeit sicherstellen.

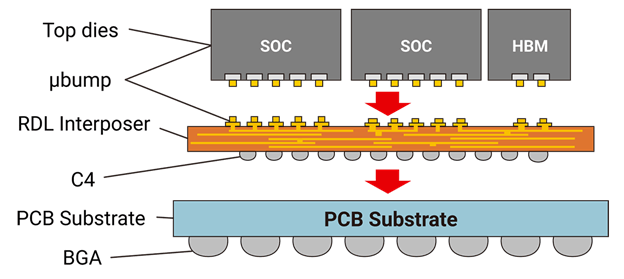

Abbildung 3: Abbildung der Cowos-R-Technologie

Eine Abbildung von Cowos-R, einer von TSMC entwickelten 3D-Integrationstechnologie, zeigt das Stapeln mehrerer Chips in einem einzigen Paket.Diese Technologie nutzt RDL, um verschiedene Chips innerhalb des Pakets zu verbinden und eine bessere Leistung und die Raumwirkungsgrad zu ermöglichen.Die Cowos-R-Technologie unterstreicht das Potenzial von RDL in fortschrittlichen Verpackungslösungen und ermöglicht die Erstellung von kompakteren und leistungsfähigeren elektronischen Geräten.Die Verwendung von RDL in der Cowos-R-Technologie zeigt, wie die Integration mehrerer Funktionen in ein einzelnes Paket unterstützt wird.Diese Integration reduziert den Gesamtstufe elektronischer Geräte und ermöglicht kompaktere und effizientere Designs.Die Fähigkeit, mehrere Chips mithilfe von RDL zu stapeln, verbessert die Leistung durch Reduzierung der Signalverzögerung und Verbesserung der Leistungsverteilung.Ingenieure müssen die gestapelten Chips akribisch ausrichten und verbinden, um sicherzustellen, dass die RDLs zuverlässige Verbindungen bieten und die Integrität der Signale und Leistungsrouten aufrechterhalten.

Vorteile der Umverteilungsschichttechnologie

Die RDL-Technologie (Umverteilungsschicht) bietet Designer eine Vielzahl von Vorteilen, die sich auf die Erstellung von Hochleistungs-, kompakten und kostengünstigen elektronischen Geräten konzentrieren.Die Einführung von RDL in Integrated Circuit (IC) hat die Entwicklung der modernen Elektronik revolutioniert und die Produktion kleinerer und effizienterer Geräte ermöglicht, ohne die Leistung zu beeinträchtigen oder die Kosten zu steigern.Im Folgenden untersuchen wir die wichtigsten Vorteile der Einbeziehung der RDL -Technologie in IC -Pakete.

Reduzierter Fußabdruck

Einer der wichtigsten Vorteile der RDL -Technologie ist die Fähigkeit, den allgemeinen Fußabdruck der elektronischen Geräte zu verringern. Durch die Integration mehrerer Chips in ein einzelnes Paket können Designer kleinere, kompaktere Geräte erstellen. Diese Größenreduzierung ist besonders vorteilhaft für räumlich begrenzte Anwendungen wie Smartphones, tragbare Technologie und Internet of Things (IoT). Die Fähigkeit, mehr Funktionen in einen kleineren Bereich zu integrieren, ist wichtig für die fortgesetzte Miniaturisierung elektronischer Geräte. Diese Kompaktheit unterstützt die Entwicklung tragbarer und benutzerfreundlicherer Geräte, die der wachsenden Nachfrage der Verbraucher nach stilvollen, bequemen Produkten entsprechen. Dies erfordert eine genaue Ausrichtung der Chips innerhalb des Pakets, um eine optimale Konnektivität und minimale Signalstörungen zu gewährleisten.

Verbesserte elektrische Leistung

Die RDL -Technologie verbessert die elektronische Leistung elektronischer Geräte erheblich.Indem RDL die Länge der Verbindungen verkürzt, die die Signalverzögerung verringert, verkürzt RDL die Länge der Verbindungen, indem der Würfel kompakter und effizienter positioniert werden kann.Dies ist besonders vorteilhaft für Anwendungen, die eine Hochgeschwindigkeitsdatenübertragung und eine präzise Signalintegrität erfordern.Darüber hinaus minimiert die RDL -Technologie die parasitäre Kapazität und Induktivität, die die Signalqualität beeinträchtigen kann.Die Behebung dieser Probleme sorgt für eine bessere Signalintegrität und die Gesamtleistung der Geräte.Designer, die RDL verwenden, können eine überlegene elektrische Leistung erzielen, was es zu einer idealen Lösung für Hochfrequenz- und Hochgeschwindigkeitsanwendungen wie Advanced Computing und Telekommunikation macht.Während der Entwurfsphase müssen die Ingenieure die RDL -Ebenen sorgfältig abbilden, um Signalwege zu optimieren und das Rauschen zu reduzieren, um sicherzustellen, dass jede Verbindung robust und zuverlässig ist.

Kostenreduzierung

Die Kostensenkung ist ein weiterer erheblicher Vorteil der RDL -Technologie.Traditionelle Methoden wie Drahtbindung und Flip-Chip-Bindung sind sowohl teuer als auch zeitaufwändig.Die RDL -Technologie optimiert den Herstellungsprozess, indem die Notwendigkeit dieser kostspieligen Bindungstechniken beseitigt wird.Darüber hinaus reduziert RDL die Anzahl der im Gerät erforderlichen Komponenten und senkt die Material- und Montagekosten weiter.Die Vereinfachung des Montageprozesses reduziert nicht nur die Kosten, sondern erhöht auch die Produktionseffizienz.Durch die Senkung der Produktionskosten und durch die Aufrechterhaltung oder sogar Verbesserung der Leistung bietet die RDL-Technologie eine kostengünstige Lösung zur Schaffung leistungsstarker ICs, für die ein kleiner Formfaktor erforderlich ist.In praktischer Hinsicht umfasst dies weniger Schritte im Montageprozess, wodurch das Potenzial für Fehler verringert und die Produktionszeiten beschleunigt werden.

Umfassende Vorteile

Die RDL -Technologie bietet erhebliche Vorteile, die sich mit den Kernherausforderungen der Designer moderner elektronischer Geräte befassen.Seine Fähigkeit, den Fußabdruck von Geräten zu reduzieren, die elektrische Leistung zu verbessern und niedrigere Kosten zu einer transformativen Technologie im Bereich der IC -Verpackung.Da die Nachfrage nach kompakteren, effizienteren und kostengünstigeren elektronischen Geräten weiter wächst, wird die Bedeutung der RDL-Technologie bei der Erfüllung dieser sich entwickelnden Bedürfnisse zunehmend ausgeprägt.Durch die Einführung von RDL können Designer die Grenzen dessen, was im elektronischen Design möglich ist, überschreiten, was zur Entwicklung innovativer Produkte führt, die den hohen Erwartungen des heutigen technologischen Marktes entsprechen.Die praktische Anwendung der RDL -Technologie beinhaltet ein detailliertes Verständnis der Materialeigenschaften, der präzisen Engineering und strengen Tests, um sicherzustellen, dass jede Komponente die höchsten Standards erbringt.

Kategorien der Umverteilung der Schichttechnologie

Die RDL-Technologie (Umverteilungsschicht) wird hauptsächlich in zwei Haupttypen eingeteilt: Fan-in und Fan-Out.Diese Kategorien unterscheiden sich durch ihre Anwendungen in der Verpackung einzelner bzw. mehrerer Stämme.

Die Fan-in RDL-Technologie wurde für die Verpackung eines einzigen Würfels entwickelt.Dieser Prozess wird häufig als Paket auf Waferebene (WLP) bezeichnet und beinhaltet ein Paket direkt auf dem Wafer.Diese Methode ist bekannt für ihre Kostenwirksamkeit und Fähigkeit, kleine und dünne Pakete zu produzieren.Der Fan-In-Ansatz ist besonders vorteilhaft in Anwendungen, in denen der Platz begrenzt ist und ein kompakter Formfaktor erforderlich ist.

In der Praxis wird die Fan-In-RDL-Technologie in mehreren genauen Schritten implementiert.Zunächst wird eine dielektrische Schicht am Wafer abgelagert, um Isolierungen bereitzustellen und die zugrunde liegenden Schaltkreise zu schützen.Als nächstes wird eine Samenschicht, die normalerweise aus Kupfer besteht, angewendet, um die Elektroplatte von Metall zu erleichtern.Die Photolithographie wird dann verwendet, um das RDL -Muster zu definieren und Wege für elektrische Verbindungen zu erzeugen.Die Metallablagerung folgt, wo Kupfer oder andere leitende Materialien auf die gemusterten Bereiche elektropliert werden, um die Verbindungen zu bilden.Nach der Metallabscheidung wird überschüssiges Material der Samenschicht weggeätzt, wodurch die definierte RDL -Struktur zurückbleibt.Schließlich ist der Wafer gewürzt, was zu individuellen Verpackungsstimmungen führt.

Diese Methode eignet sich für verschiedene Anwendungen, einschließlich Sensoren, MEMS -Geräte, RF -Geräte, Mikroprozessoren und Speichergeräten.Diese Komponenten profitieren von der kompakten und effizienten Verpackung, die von Fan-In RDL bereitgestellt wird, was eine zuverlässige Leistung und einen minimalen Fußabdruck gewährleistet.Ingenieure und Techniker, die mit Fan-in RDL arbeiten, müssen jeden Schritt sorgfältig verwalten, um Präzision und Funktionalität aufrechtzuerhalten.

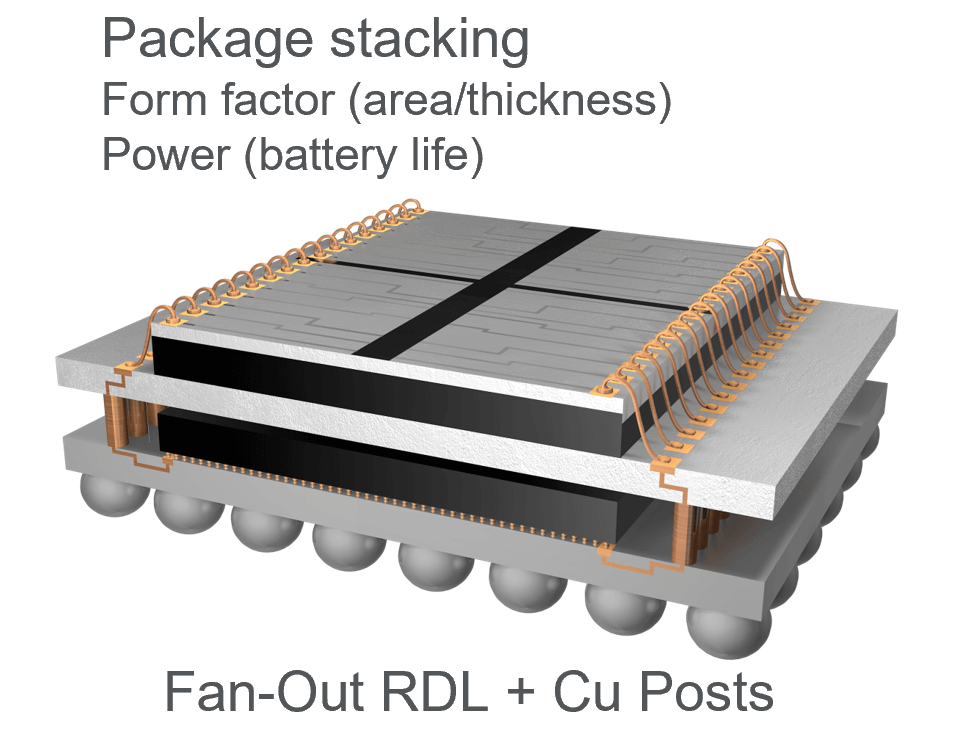

Die Fan-Out RDL-Technologie, auch als Wafer-Level Fan-Out (WLFO) bekannt, wird für die Verpackung mehrerer Stämme verwendet.In diesem Prozess werden ein Paket für einen rekonstituierten Wafer erstellt, der durch Einbetten mehrerer Stanze in eine Formmasse gebildet und dann als einzelner Wafer neu verarbeitet wird.Die Fan-Out-RDL-Technologie ist für ihre Fähigkeit erkannt, Hochleistungspakete mit einem kleinen Formfaktor zu erstellen, was sie ideal für komplexe und anspruchsvolle Anwendungen macht.

Abbildung 4: Fan-Out

Die Implementierung der Fan-Out-RDL-Technologie umfasst mehrere detaillierte Schritte.Zunächst werden individuelle Stanze in eine Form gegeben und mit einer Formmasse eingekapselt, um einen rekonstituierten Wafer zu bilden.Dieser Prozess, der als Waferrekonstitution bezeichnet wird, bietet einen größeren Arbeitsbereich und ermöglicht die Integration mehrerer Stämme.Sobald der wiederherstellte Wafer gebildet ist, wird er ähnliche Verarbeitungsschritte wie ein herkömmlicher Wafer durchgeführt.Eine dielektrische Schicht wird abgelagert, gefolgt von der Anwendung einer Samenschicht.Die Photolithographie wird verwendet, um das RDL -Muster zu definieren, und die Metallablagerung erzeugt die Verbindungen.Der rekonstituierte Wafer wird dann gewürzt, um einzelne Pakete mit mehreren Stanzen zu erstellen.

Diese Technologie eignet sich für Anwendungen wie Grafikprozessoren, System-On-Chip-Geräte (SOC), Speichergeräte, Leistungsgeräte und LED-Geräte.Der Fan-Out-Ansatz bietet eine verbesserte Leistung aufgrund der kürzeren Verbindungen und eines verbesserten thermischen Managements, die für leistungsstarke Anwendungen vorteilhaft sind.Die erhöhte Oberfläche des rekonstituierten Wafers ermöglicht auch komplexere Routing und höhere Integrationsdichte, was fortschrittliche elektronische Konstruktionen zugute kommt.

Sowohl Fan-In- als auch Fan-Out-RDL-Technologien bieten einzigartige Vorteile, die auf unterschiedliche Verpackungsbedürfnisse zugeschnitten sind.Fan-In RDL ist ideal für Einzelpersonen, die kompakte und effiziente Verpackungen benötigen, während Fan-Out-RDL in Multi-Die-Anwendungen, die eine hohe Leistung und kleine Formfaktoren benötigen, übertroffen werden.Das Verständnis der spezifischen Anforderungen des elektronischen Geräts und der Auswahl der geeigneten RDL-Technologie gewährleistet eine optimale Leistung und Kostenwirksamkeit bei der IC-Verpackung.Praktische menschliche Betriebserfahrungen mit RDL -Technologien beinhalten sorgfältige Liebe zum Detail und Präzisionstechnik, um die gewünschten Ergebnisse zu erzielen.

Schritte im Prozess der Umverteilung Schicht (RDL)

Die RDL -Technologie (Umverteilungsschicht) umfasst eine komplexe Reihe von Schritten, einschließlich dielektrischer Ablagerung, Metallabscheidung, Strukturierung und Ätzen. Diese Schritte erstellen erweiterte Verpackungslösungen für Halbleitergeräte. Es gibt verschiedene Prozessflüsse für Fan-in RDL und Fan-Out-RDL, und jeder Prozessfluss ist speziell auf die bestimmten Verpackungsanforderungen zugeschnitten.

Die Fan-In-RDL-Technologie ist maßgeblich an der Entwicklung fortschrittlicher Verpackungslösungen wie dem WLCSP-Design (Wafer-Level-Chip-Skala-Verpackungen) und dem System-in-Package-Design (SIP-Designs) beteiligt.Diese Methode verbessert die Integrationsniveaus, reduziert Formfaktoren und verbessert die Leistung der Halbleiter.Der Prozess umfasst mehrere erforderliche Schritte, um die gewünschten Paketeigenschaften zu erreichen.

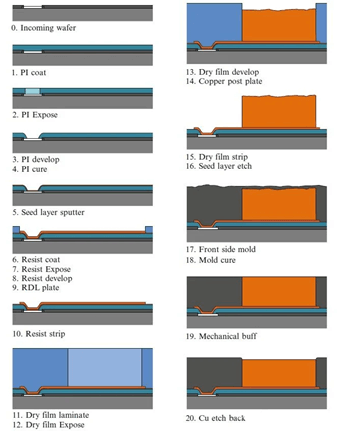

Abbildung 5: Fan-in RDL-Prozessfluss

Der Fan-in RDL-Prozess beginnt mit einem eingehenden Wafer, der sich einer Reihe präziser Operationen unterzieht.Zunächst wird der Wafer in Schritt 1 mit einem photoresistischen Isolator (PI) beschichtet. Diese Schicht ist in Schritt 2 einem ultravioletten Licht ausgesetzt, um das gewünschte Muster zu übertragen, gefolgt von der Entwicklung in Schritt 3, um die nicht exponierten Bereiche zu entfernen.Der PI wird dann in Schritt 4 geheilt, um das Material zu härten.Als nächstes wird eine Samenschicht in Schritt 5 auf den Wafer gesputscht und dient als Basis für die nachfolgende Metallablagerung.Der Wafer wird in Schritt 6 mit Resist beschichtet, der dann durch Exposition (Schritt 7) und Entwicklung (Schritt 8) strukturiert wird.Die RDL wird in Schritt 9 elektropliert und bildet die Verbindungen.

Nach der RDL -Formation wird der Resist in Schritt 10 abgezogen, und ein trockener Film wird in Schritt 11 auf den Wafer laminiert. Dieser Film ist freigelegt (Schritt 12) und entwickelt (Schritt 13), um VIAS oder andere Strukturen zu erzeugen.Kupferpfosten werden in Schritt 14 auf den Wafer verteilt und bieten robuste elektrische Verbindungen.Der Trockenfilm wird dann in Schritt 15 entfernt. Die Samenschicht ist in Schritt 16 weggeätzt und bleibt nur die gewünschten Kupferstrukturen.In Schritt 17 entsteht eine Frontform, die den in Schritt 18 geheilten Würfel abgehärtet hat. Der Wafer wird in Schritt 19 mechanisch gepackt, um eine glatte Oberfläche zu gewährleisten, und das überschüssige Kupfer wird in Schritt 20 zurückgeätzt, wobei der Lüfter abgeschlossen wird-in RDL -Prozess.

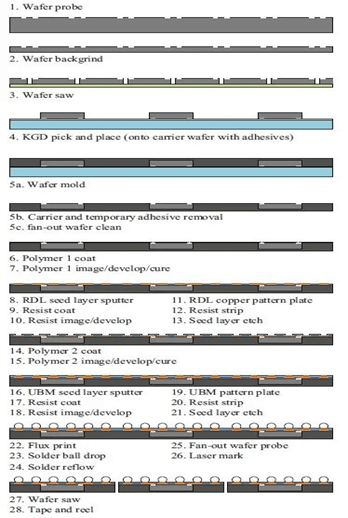

Der Fan-Out-RDL-Prozess, auch als Fan-Out (WLFO) auf Waferebene bekannt, wird verwendet, um kleinere, höhere Performance-Chip-Pakete mit mehr Verbindungen zu erstellen.Dieser Prozess beinhaltet die Bildung eines rekonstituierten Wafers durch Einbettung mehrerer Stanze in eine Formmasse.

Der Fan-Out-RDL-Prozess beginnt mit Waferuntersuchung (Schritt 1), um zu testen und sicherzustellen, dass der Wafer den erforderlichen Spezifikationen entspricht.In Schritt 2 wird der Wafer zurückgeschleift, um seine Dicke zu verringern.Der Wafer wird dann in Schritt 3 in individuelle Sterben gesägt. Bekannte gute Sterben (KGD) werden gepflückt und in Schritt 4 auf einen Trägerwafer gelegt.

Abbildung 6: Fan-Out-RDL-Prozessfluss (Umverteilung der Umverteilung)

Schritt 5 umfasst mehrere Unterschritte: 5a) die Waferform, wobei die Stanze in einem dielektrischen Material zur Bildung der Lüfterstruktur eingekapselt sind.5b) Entfernung des Trägers und vorübergehender Klebstoff;und 5c) Reinigen Sie den Fan-Out-Wafer, um Restpartikel zu beseitigen.Als nächstes wird in Schritt 6 eine Polymerschicht angewendet, gefolgt von Bildgebung, Entwicklung und Heilung (Schritt 7), um die RDL -Struktur zu erstellen.

In Schritt 8 wird eine dünne Samenschicht auf das Polymer gesputtert, gefolgt von einer Resistbeschichtung (Schritt 9), der Bildgebung und Entwicklung des Resists (Schritt 10) und der elektroplanten Kupfer auf die freiliegende Samenschicht, um das RDL -Muster zu bilden (Schritt 11).Der Resist wird in Schritt 12 entfernt und die nicht benötigte Samenschicht ist in Schritt 13 geätzt.

Eine zweite Polymerschicht wird in Schritt 14 aufgetragen, in Schritt 15 gemustert und geheiltBilden Sie die Unter-Bump-Metallurgie (UBM) Struktur (Schritt 19).Der Resist wird in Schritt 20 entfernt und die Samenschicht in Schritt 21 geätzt.

In Schritt 22 werden Fluss auf die UBM -Pads aufgetragen, gefolgt von Lötkugeln auf diese Pads in Schritt 23. Die Lötkugeln werden in Schritt 24 reflowiert, um elektrische Verbindungen herzustellen.Der Fan-Out-Wafer wird in Schritt 25, Lasermarkierung zur Identifizierung in Schritt 26, endgültige Tests durchgeführt und wird dann in Schritt 27 in einzelne Pakete gesägt. Schließlich werden die Pakete in Schritt 28 auf einer Rolle für den Versand montiert.

Sowohl Fan-in- als auch Fan-Out-RDL-Prozesse bieten unterschiedliche Vorteile, die auf unterschiedliche Verpackungsbedürfnisse zugeschnitten sind.Fan-in RDL eignet sich für Einzelpersonen, die kompakte Verpackungen erfordern, während Fan-Out-RDL in Multi-Die-Anwendungen mit hohen Leistung und Konnektivitätsanforderungen ausgestattet ist.Die Beherrschung dieser Prozesse beinhaltet eine präzise Kontrolle und das Engineering, um optimale Ergebnisse bei der IC -Verpackung zu gewährleisten.

RDL -Anwendung auf erweiterte Verpackungen

Die RDL-Technologie (Umverteilungsschicht) ist ein Eckpfeiler fortschrittlicher Verpackungen, insbesondere in Fan-in-Wafer-Paket (FIWLP) und FOWLP-Technologien (Fan-Out-Out-Out-Paket).Die Entwicklung von RDL ermöglichte es Verpackungsanlagen, direkt mit Wafergießereien zu konkurrieren, insbesondere in der Fan-Out-Verpackungsdomäne.Durch die Nutzung von RDL können Eingangs-/Ausgangspads (IOPADs) in verschiedene Arten von Paketen auf Waferebene integriert werden, sei es in FIWLP oder Fowlp.In FIWLP werden alle Unebenheiten direkt auf dem Würfel entwickelt, wobei Verbindungen durch die Metalllinien von RDL erleichtert werden, was zu einem integrierten Schaltkreis (IC) nahezu die gleiche Größe wie die Sterbe führt.Umgekehrt können Beulen bei Fowlp über den Stempel hinausgehen und ein verpacktes IC ungefähr 1,2 -mal größer als der Würfelbereich erzeugen.

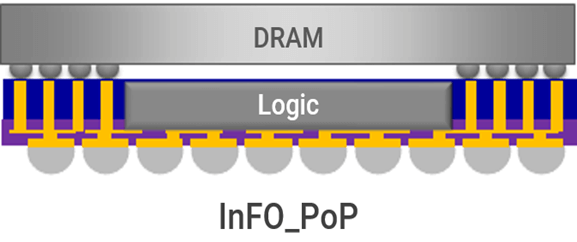

Die Bedeutung von RDL wird in der 2,5D -Verpackung weiter unterstrichen.Über den Silizium-Substrat hinaus veranschaulicht die integrierte Verpackung von TSMC (TSMC) im Silizium-Substrat (TSVs) im Silizium-Substrat.Bei diesem Ansatz werden ein oder mehrere bloße Stanze auf einen Träger platziert und in einen wiederhergestellten Wafer aus Formmaterial eingebettet.Anschließend werden RDL -Verbindungen und dielektrische Schichten auf dem Wafer unter Verwendung eines Prozessablaufs „Chip First“ konstruiert.Diese Methode ist besonders vorteilhaft für Single-Die-Info-Konfigurationen, die eine hohe Beulenzählungen bieten.Die RDL-Linien erstrecken sich vom Chipbereich nach außen und erzeugen eine "Fan-Out" -Topologie, die die Leistung verbessert, indem mehr Routing-Raum und eine bessere Wärmeabteilung bereitgestellt werden.

Praktische Implementierung von RDL in FIWLP und Fowlp

Die Implementierung von RDL in diesen Verpackungstechnologien beinhaltet mehrere detaillierte Schritte.Für FIWLP beginnt der Prozess mit der Vorbereitung des eingehenden Wafers, der eine dielektrische Schichtablagerung durchläuft, um den Würfel zu isolieren und zu schützen.Darauf folgt die Sputtermetallschichten und strukturiert sie, um die RDL -Strukturen zu bilden, die den Würfel mit den Unebenheiten verbinden.Diese Unebenheiten werden dann auf dem Würfel gezüchtet, um robuste elektrische Verbindungen zu gewährleisten.

Im Gegensatz dazu beginnt Geflügel mit der Platzierung von bekannten Gutenmotiven (KGD) auf einen rekonstituierten Wafer.Dieser Wafer wird gebildet, indem die Stanze in eine Formmasse eingebettet werden, gefolgt von ähnlichen Schritten der Ablagerung der Dielektrizität und der Metallschicht, um die RDL -Strukturen zu erzeugen.Die Flexibilität, Beulen über den Flächenbereich in Geflügel hinaus zu erweitern, ermöglicht komplexere Designs und höhere Integrationsniveaus.Dieser Vorgang beginnt mit der Waferprüfung, um sicherzustellen, dass der Wafer den erforderlichen Spezifikationen entspricht.Der Wafer wird dann zurückgelegt, um seine Dicke zu verringern, und wird anschließend zu individuellen Stimmungen gesägt.Diese Stimmungen werden dann mit Klebstoff auf einen Trägerwafer gelegt.Die folgenden Schritte umfassen die Einkapselung der Würfel in einem dielektrischen Material, um die Fan-Out-Struktur zu bilden, den Träger zu entfernen und den vorübergehenden Klebstoff zu entfernen und den Fan-Out-Wafer zu reinigen.

Detaillierte operative Schritte für FIWLP und Fowlp

Für FIWLP wird nach der anfänglichen dielektrischen Ablagerung und der Metallspotterung die Photolithographie verwendet, um die RDL zu mustert.Der Strukturierungsprozess umfasst die Anwendung eines Photoresists, das Aussetzen des Ultravioletten Lichts, um das Muster zu übertragen, den Photoresist zu entwickeln, um die gewünschten Bereiche aufzudecken, und das exponierte Metall für die Erzeugung der RDL -Wege.Nach der Bildung von RDL wird ein trockener Film auf den Wafer laminiert, freigelegt, entwickelt und strukturiert, um VIAS oder andere Strukturen für elektrische Verbindungen zu erzeugen.Kupferpfosten werden dann auf den Wafer elektropliert, wobei robuste Verbindungen hergestellt werden, gefolgt von der Ätzen der Samenschicht und dem Einkapselung des Würfels mit einer Vorderseite.Zu den letzten Schritten gehören das Aushärten der Form, das mechanisch ebnete Gewehr, um eine glatte Oberfläche zu gewährleisten, und das Ätzen von überschüssigem Kupfer, um den Prozess abzuschließen.

Beim Vorbereitungsverfahren werden nach der anfänglichen Wafervorbereitung, einschließlich des Rückenschleifens und des Würfels, die guten Sterben auf einen Trägerwafer mit Klebstoff gelegt.Der rekonstituierte Wafer wird dann gebildet, indem die Würfel in einer Formmasse eingekapselt werden.Darauf folgt eine Polymerschicht, die dann strukturiert und geheilt wird, um die RDL -Struktur zu erstellen.Eine Samenschicht wird auf das Polymer gesputscht, gefolgt von Resist -Beschichtung, Bildgebung, Entwicklung und Elektrierung, um das RDL -Muster zu bilden.Der Resist wird entfernt und die nicht benötigte Samenschicht geätzt.Dieser Vorgang wird mit einer anderen Polymerschicht und einer Saatgutschicht wiederholt, um die UBM-Struktur (UBM-Metallurgie) zu bilden.Schließlich wird der Fluss auf die UBM-Pads angewendet, Lötkugeln werden platziert und reflowiert, um elektrische Verbindungen herzustellen, und der Fan-Out-Wafer wird endgültige Tests, Lasermarkierung und das Würfeln in einzelne Pakete durchgeführt.

Erweiterte RDL -Anwendungen in der 2.5D -Verpackung

Die Komplexität von RDL in 2,5D -Paketen, wie z. B. die Informationen von TSMC, wird durch die komplexen Schicht- und Verbindungstechniken demonstriert. Nachdem der Chip in den rekonstituierten Wafer eingebettet ist, werden mehrere RDL -Schichten gebaut, die jeweils sorgfältig gemustert und geätzt werden, um Verbindungen zu bilden. Dieser Vorgang verbindet den Chip nicht nur mit externen Schaltkreisen, sondern verbessert auch die elektrische Gesamtleistung durch Reduzierung von Widerstand und Induktivität. Das resultierende Paket ist hocheffizient und bietet eine verbesserte Leistungsverteilung und Signalintegrität, was für leistungsstarke Computeranwendungen wichtig ist.

Abbildung 7: Die integrierte Fan-Out (Info-Verpackungstechnologie von TSMC)

Die Anwendung der RDL -Technologie in fortschrittlichen Packungen wie FIWLP-, Fowlp- und 2.5D -Konfigurationen wie TSMCs Info hat die Halbleiterverpackungsbranche revolutioniert.RDL ermöglicht die Erstellung kompakter, leistungsstarker und hochintegrierter Pakete, die den wachsenden Anforderungen der modernen Elektronik entsprechen.Die detaillierten und genauen Schritte, die an RDL -Prozessen beteiligt sind, unterstreichen die Bedeutung von Ingenieurkompetenz und sorgfältiger Ausführung, um optimale Ergebnisse bei der IC -Verpackung zu erzielen.

Bewertung von RDL- und anderen IC -Verpackungstechnologien

Die Technologien für integrierte Schaltung (IC) haben sich erheblich weiterentwickelt und bieten verschiedene Methoden zum Verbinden und Schutz von Halbleiterchips an.Jede Technologie verfügt über unterschiedliche Prozesse, Vorteile, Nachteile und Anwendungen, die den spezifischen Anforderungen elektronischer Geräte erfüllen.Im Folgenden vergleichen wir die RDL -Technologie (Umverteilungsschicht) mit anderen vorherrschenden IC -Verpackungstechnologien, um ihre Unterschiede und Anwendungsfälle hervorzuheben.

Die Drahtbindung ist eine herkömmliche Methode, die das IC mit feinen Drähten mit der PCB verbindet.Es ist bekannt für seine niedrigen Kosten, Flexibilität und Zuverlässigkeit.Es fehlt jedoch die Leistung, die für Hochfrequenz- und Hochleistungsanwendungen erforderlich ist, was es für einfachere, weniger anspruchsvolle elektronische Geräte geeignet ist.Die Drahtbindung bleibt in Anwendungen beliebt, bei denen Kosten und Zuverlässigkeit vor der Leistung priorisiert werden.

Bei der Flip-Chip-Bindung wird die Sterblichkeit mit Lötplatten an das Substrat an das Substrat verbinden.Diese Methode liefert eine hohe Leistung und eine geringe Induktivität, was sie ideal für Anwendungen macht, die überlegene elektrische Eigenschaften erfordern.Die Flip-Chip-Bindung erfordert jedoch eine genaue Ausrichtung und ist teurer als die Drahtbindung.Es wird üblicherweise in Hochleistungs-Computing und Telekommunikation verwendet.

Silizium -Vias (TSVs) erzeugen vertikale Verbindungen durch ein Siliziumsubstrat und bieten eine höhere Leistung und kleinere Formfaktoren.Die TSV -Technologie unterstützt die 3D -Stapel von Chips und erhöht damit die Leistung und die Integrationsdichte. Obwohl TSV viele Vorteile hat, beinhaltet es komplexe und kostspielige Herstellungsprozesse, sodass es für High-End-Anwendungen in Bezug auf Leistung und räumliche Sparung geeignet ist.

Das Chip-Scale-Paket (CSP) ersetzt den herkömmlichen Bleirahmen durch ein Substrat, was zu einem kompakten Formfaktor und einem E/A mit hoher Dichte führt.CSP ist kostengünstig und unterstützt ein hohes Maß an Integration.Es hat jedoch Einschränkungen hinsichtlich der I/A -Kapazität und der mechanischen Spannungsbeständigkeit.CSP wird häufig in der Unterhaltungselektronik verwendet, bei der Größe und Kosten wichtige Faktoren sind.

Die integrierte Fan-Out (Info) -Technologie integriert mehrere Chips in ein einzelnes Paket und erweitert E/O-Punkte über den Chip hinaus. Es bietet eine hohe Dichte und einen geringen Stromverbrauch, ist jedoch komplex und kostspielig.Informationen werden in fortschrittlichen Anwendungen wie Smartphones und Hochleistungs-Computing verwendet, bei denen die Dichte und die Stromversorgung von Bedeutung sind.

Hochbandbreite Memory (HBM) verwendet 3D -Stapel, um einen hohen Bandbreiten und einen geringen Stromverbrauch zu erzielen.Es ist ideal für Hochleistungs-Computing und Anwendungen, die einen signifikanten Datendurchsatz erfordern.HBM ist jedoch teuer und hat eine begrenzte Skalierbarkeit, was für bestimmte Anwendungen ein Nachteil sein kann.

Chip on Wafer on Substrat (Cowos) integriert Chips auf einem Siliziumwafer und bietet eine hohe Bandbreite und heterogene Integration.Diese Technologie unterstützt komplexe und leistungsstarke Anwendungen, beinhaltet jedoch einen komplexen und kostengünstigen Herstellungsprozess.Cowos wird in High-End-Computing und Telekommunikation verwendet.

Die RDL -Technologie (Umverteilungsschicht) erzeugt eine gemusterte Metallschicht auf einer dielektrischen Schicht, die eine hohe Dichte und eine flexible Routing bietet.Während RDL Einschränkungen bei der Leistungsbeschaffung und der mechanischen Spannungsanfälligkeit aufweist, zeichnet sie sich aus der Fähigkeit aus, kompakte und effiziente Verpackungslösungen bereitzustellen.RDL wird in der modernen Elektronik häufig verwendet, einschließlich Smartphones und IoT -Geräten, bei denen eine hohe Dichte und Leistung erforderlich sind.

Die Bump-Technologie legt Metallbeule auf dem Chip ab und bietet einen kostengünstigen und einfachen Herstellungsprozess.Es bietet jedoch eine begrenzte Leistung für hochfrequente und hohe Leistungsanwendungen.Die Bump -Technologie wird häufig in weniger anspruchsvollen Anwendungen eingesetzt, bei denen Kosten und Einfachheit priorisiert werden.

Abschluss

Jede IC -Verpackungstechnologie hat einzigartige Vorteile, die für verschiedene Anwendungen geeignet sind. Daher wird die Aktivierungstechnologie ausgewählt, um die Anforderungen des spezifischen elektronischen Geräts zu erfüllen. Drahtbindungs- und Stumpentechnologien sind kostengünstig und für weniger anspruchsvolle Verwendungen wie Unterhaltungselektronik und Automobilanwendungen zuverlässig. Aufgrund ihrer Leistungsbeschränkungen arbeiten sie jedoch in hochfrequenten und hohen Leistungsszenarien schlecht ab. Fortgeschrittene Ansätze wie Durch-Silicon-VIAS (TSV), Integrated Fan-Out (Info), High-Bandwidth Memory (HBM) und Chip-on-Wafer-On-Substrat (Cowos) bieten überlegene Leistungs- und Integrationsfunktionen. Diese Technologien sind für Anwendungen von Vorteil, die hohe Geschwindigkeit, hohe Leistung und kompaktes Formfaktor erfordern, wie z. B. Hochleistungs-Computing und Grafikverarbeitung. Ihre Komplexität und höhere Kosten können jedoch Hindernisse für die weit verbreitete Einführung bei kostenempfindlichen Anwendungen sein.

Das Verständnis der einzigartigen Vorteile und Einschränkungen der einzelnen IC -Verpackungstechnologie ermöglicht es Designer und Ingenieuren, fundierte Entscheidungen zu treffen, die Leistung, Kosten und Komplexität ausgleichen.Die Drahtbindung und die Beule-Technologie bleiben für weniger anspruchsvolle Anwendungen relevant, während fortschrittliche Techniken wie TSV, Info, HBM und Cowos den Bedarf an Hochleistungsbedürfnissen gerecht werden.Die RDL -Technologie mit ihrem Gleichgewicht zwischen hoher Dichte und Kompaktheit spielt in der nächsten Generation elektronischer Geräte eine entscheidende Rolle und unterstützt Innovationen in verschiedenen Sektoren.Die Zukunft der IC -Verpackung wird wahrscheinlich in diesen Technologien weiterentwickelt, die durch das unerbittliche Streben nach besserer Leistung, kleineren Formfaktoren und einer größeren Effizienz angetrieben werden.

Häufig gestellte Fragen [FAQ]

1. Was ist die RDL -Technologie (Umverteilungsschicht)?

RDL -Technologie (Umverteilung Schicht) beinhaltet das Hinzufügen einer gemusterten Metallschicht auf einer dielektrischen Schicht in der IC -Verpackung (IC).Dieser Prozess stammt und optimiert die elektrischen Verbindungen und verbessert die Dichte und Leistung der ICs.Im Wesentlichen ermöglicht es eine bessere Nutzung des Raums und effizientere elektrische Wege, wodurch die Gesamtfunktionalität des Chips verbessert wird.

2. Wie ist die Kabelbindung mit anderen IC -Verpackungsmethoden verglichen?

Drahtbindung ist eine kostengünstige und zuverlässige Methode zum Anschließen von ICs mit ihren Paketen.Es wird in vielen Anwendungen weit verbreitet, da es unkompliziert und kostengünstig ist.Es funktioniert jedoch nicht gut in hohen Frequenz- und Hochleistungsszenarien.Fortgeschrittene Methoden wie Flip-Chip-Bonding und Through-Silicon über (TSV) bieten diesen anspruchsvollen Anwendungen eine überlegene Leistung, sind jedoch teurer und komplexer für die Implementierung.

3. Was sind die Vorteile der Flip-Chip-Bindung?

Die Flip-Chip-Bindung bietet hohe Leistung, Eingang/Ausgang (E/O) mit hoher Dichte und niedrige Induktivität, was es ideal für Hochgeschwindigkeitsdatenkommunikation und Hochleistungsanwendungen ist.Diese Methode nutzt den Raum auf dem Chip besser und verbessert die thermische und elektrische Leistung.Es ermöglicht kompaktere und effizientere Konstruktionen im Vergleich zur herkömmlichen Drahtbindung.

4. Welche Herausforderungen haben Thry-Silicon über (TSV) -Technologie (TSV)?

Durch Silizium über (TSV) -Technologie verbessert die Signalübertragung und reduziert den Stromverbrauch, indem kürzere Verbindungslängen und höhere Leistung bereitgestellt werden. Aufgrund seines komplexen und teuren Herstellungsprozesses stellt es jedoch erhebliche Herausforderungen. Präzise vias und füllen Sie die thermische und mechanische Spannung, um die Verbindungsintegrität aufrechtzuerhalten.

5. Warum wird die RDL -Technologie in der modernen Elektronik als transformativ angesehen?

Die RDL-Technologie ist transformativ, da sie die Erstellung kompakter, leistungsstarker und effizienter IC-Pakete ermöglicht.Es ermöglicht kompliziertere und dichtere Verbindungen innerhalb des Chips, was zu einer besseren elektrischen Leistung und Raumeffizienz führt.Dies macht die RDL -Technologie zu einer wertvollen Lösung für fortschrittliche Anwendungen, die eine Miniaturisierung und eine verbesserte Leistung erfordern.

Verwandter Artikel

-

May 29 20247408 Die Vielseitigkeit integrierter Schaltungen

Der 7408 Integrated Circuit (IC) ist für die digitale Elektronik von wesentlicher Bedeutung und enthält vier unabhängige zwei Eingänge und Tore.Je... -

May 24 2024Umfassende Leitfaden zur Netzspannung

Die Versorgungsspannung ist die Grundlage für das Entwerfen und Betrieb elektronischer Schaltungen, um die ordnungsgemäße Funktionsweise von Kompon...

Verwandte -Produkte

CM200DY-24NF

IGBT MOD 1200V 200A 1130W

TLC072CDGN

IC OPAMP GP 2 CIRCUIT 8HVSSOP

TPS3808G25DRVR

IC SUPERVISOR 1 CHANNEL 6WSON

AD9957BSVZ-REEL

IC DDS 1GHZ 14BIT 100TQFP

MPY100AM

BB Can

STM32F070F6P6

IC MCU 32BIT 32KB FLASH 20TSSOP

G5V-2-24VDC

G5V-2-24VDC OMRON

GM1501-BD

GENESIS BGA

TMP19A44FDAXBG7GR3

TMP19A44FDAXBG7GR3 TOSHIBA

GDT1668CO

GDT1668CO G-DESIGN

MAX5291BEUE

IC DAC 12BIT V-OUT 16TSSOP

CDP6818AQ

INTERSI PLCC