Alle Kategorien

-

Integrierte schaltkreise (ICS)

Integrierte schaltkreise (ICS)

- Schnittstelle - Sensor, kapazitive Berührung(642)

- Spezialisierte ICS(12302)

- PMIC-Spannungsregler-besonderer Zweck(5644)

- PMIC-Spannungsregler-lineare Regler(793)

- PMIC-Spannungsregler-linear + Switching(1829)

- PMIC-Spannungsregler-linear(70981)

- PMIC-Spannungsregler-DC DC Switching Regulators(39569)

- PMIC-Regler-DC-DC-Switching-Controller(13507)

- PMIC-Spannungs-Referenz(9453)

- PMIC-v/f und f/v-Wandler(145)

- PMIC-Thermal Management(592)

- PMIC-Supervisor(47946)

- PMIC-RMS bis DC-Wandler(170)

- PMIC-Netzteil-Controller, Monitore(2104)

- PMIC-Power over Ethernet (PoE) Controller(1008)

- PMIC-Power Management-spezialisierte(7722)

- PMIC-Netzschalter, Treiber laden(7706)

- PMIC-PFC (Power Factor Correction)(1222)

- PMIC oder Steuerungen, ideale Dioden(705)

- PMIC-Motor-Treiber, Regler(4712)

- PMIC-Beleuchtung, Ballast-Regler(560)

- PMIC-LED-Treiber(7282)

- PMIC-Laser-Treiber(573)

- PMIC-Hot-Swap-Controller(2816)

- PMIC-Gate-Treiber(7083)

- PMIC-voll, Half-Bridge-Treiber(1342)

- PMIC-Energy Messung(654)

- PMIC-Display-Treiber(1435)

- PMIC-derzeitige Regulierung/Management(1481)

- PMIC-Batterie-Management(5553)

- PMIC-Ladegeräte(3831)

- PMIC-AC DC Konverter, Offline Schalter(4905)

- Memory-Controller(358)

- Memory-Konfigurations-Proms für FPGAs(639)

- Speicher-Akkus(13)

- Erinnerung(65694)

- Logic-universelle Bus-Funktionen(706)

- Logic-Übersetzer, Level-Shifter(2854)

- Logik-Specialty Logic(1870)

- Logik-Signal-Schalter, Multiplexer, Decoder(9420)

- Logic-Shift-Register(2665)

- Logic-Parity Generatoren und Checkers(335)

- Logic-multivibratoren(831)

- Logik-Latches(3658)

- Logik - Tore und Wechselrichter - Multifunktion, konfigurierbar(1687)

- Logik-Tore und Wechselrichter(16453)

- Logic-Flip Flops(7780)

- Logik-FIFOs Speicher(4240)

- Logik-Zähler, Trennlinien(3456)

- Logik-Vergleichsoperator(592)

- Logik-Puffer, Treiber, Receiver, Transceiver(17835)

- Linear-Video-Verarbeitung(2909)

- Linear-Vergleichsoperator(5084)

- Linear-analoge Multiplikatoren, Trennwände(263)

- Linear-Verstärker-Video Amps und Module(1905)

- Linear-Verstärker-Spezial-Zweck(1856)

- Linear - Verstärker - Instrumentierung, OP -Verstärker, Pufferverstärker(34236)

- Linear-Verstärker-Audio(4567)

- Interface-Voice Record und Playback(556)

- Schnittstelle - UARTs (Universal Asynchronous Receivers -Sender)(1236)

- Schnittstelle-Telecom(4467)

- Interface-spezialisierte(4833)

- Interface-Signal Terminatoren(333)

- Interface-Signal-Puffer, Repeater, Splitter(1449)

- Interface-Serializer, Deserializer(1480)

- Schnittstellen-Sensor und Detektor-Interfaces(1524)

- Interface-Module(169)

- Interface-Modems-ICS und Module(407)

- Interface-e/a-Expander(1136)

- Interface-Filter-aktiv(1226)

- Interface-Encoder, Decoder, Konverter(714)

- Interface-Treiber, Receiver, Transceiver(20755)

- Interface-Direct Digital Synthesis (DDS)(117)

- Interface-Controller(3628)

- Interface-Codecs(1676)

- Schnittstelle - Analoge Switches, Multiplexer, Demultiplexer(12567)

- Schnittstelle-analoge Schalter-spezieller Zweck(2533)

- Embedded-System on Chip (SoC)(4496)

- Embedded-PLDs (programmierbare Logik-Vorrichtung)(971)

- Embedded-Mikroprozessoren(10083)

- Embedded-Mikrocontroller-anwendungsspezifische(2275)

- Embedded-Mikrocontroller(99285)

- Eingebettet - Mikrocontroller, Mikroprozessor, FPGA -Module(1527)

- Eingebettet - FPGAs (Feldprogrammiergate -Array) mit Mikrocontrollern(81)

- Embedded-FPGAs (Field Programmable Gate Array)(27748)

- Embedded-DSP (Digital Signal Processors)(4081)

- Eingebettet - CPLDs (komplexe programmierbare Logikgeräte)(5187)

- Datenerfassung-Touch Screen Controller(1210)

- Datenerfassung-Digital to Analog Converter (DAC)(14419)

- Datenerfassung-digitale Potentiometer(6250)

- Datenerfassung-analog zu Digital Converters (ADC)(17776)

- Datenerfassung-analoges Frontend (AFE)(787)

- Datenerfassung-MDE/DACs-spezieller Zweck(3043)

- Clock/Timing-Uhren in Echtzeit(2446)

- Uhr/Timing - programmierbare Timer und Oszillatoren(23469)

- Clock/Timing-IC-Akkus(4)

- Takt/Timing-Delay Lines(1049)

- Uhr/Timing - Uhrengeneratoren, PLLS, Frequenzsynthesizer(32775)

- Clock/Timing-Clock Puffer, Treiber(4568)

- Clock/Timing-anwendungsspezifische(8652)

- Audio Spezial-Zweck(1564)

-

Diskrete Halbleiter-Produkte

Diskrete Halbleiter-Produkte

- Aktuelle Regulierung - Dioden, Transistoren(1090)

- Transistoren-besonderer Zweck(226)

- Transistoren-programmierbare Unijunction(48)

- Transistoren-jfets(1558)

- Transistoren-IGBTs-Einzel(4799)

- Transistoren-IGBTs-Module(63420)

- Transistoren-IGBTs-Arrays(26)

- Transistoren-FETs, MOSFETs-Einzel(48330)

- Transistoren-FETs, MOSFETs-RF(4903)

- Transistoren-FETs, MOSFETs-Arrays(6641)

- Transistoren-Bipolar (BJT)-einzeln, Pre-biased(4539)

- Transistoren-Bipolar (BJT)-Einzel(25800)

- Transistoren-Bipolar (BJT)-RF(2087)

- Transistoren-bipolare (BJT)-Arrays, Pre-biased(2115)

- Transistoren-bipolare (BJT)-Arrays(2310)

- Thyristor-triacs(4044)

- Thyristoren-SCRs-Module(3967)

- Thyristoren-SCRs(5436)

- Thyristoren-diacs, sidacs(319)

- Power Driver Module(1627)

- Dioden-zenerdioden-Einzel(87483)

- Dioden-zenerdioden-Arrays(2619)

- Dioden - variable Kapazität (Varik, Varaktoren)(1200)

- Dioden-RF(2753)

- Dioden-Gleichrichter-Einzel(67528)

- Dioden-Gleichrichter-Arrays(20581)

- Dioden-Brücke-Gleichrichter(11700)

-

RF/if und RFID

RF/if und RFID

- SIM -Karten für Abonnenten -Identifikationsmodul (SIM)(77)

- RF -Zirkulatoren und Isolatoren(1742)

- RFID, RF-Zugang, Monitoring-ICS(1550)

- RFID Transponder, Tags(747)

- RFID Lesegeräte(464)

- RFID -Bewertungs- und Entwicklungskits, Boards(30)

- RFID Antennen(329)

- RFI und EMI - Abschirm- und Absorbungsmaterialien(6444)

- HF und EMI-Kontakte, Fingerstock und Dichtungen(7497)

- RF Transmitter(668)

- RF Transceiver Module(6900)

- RF-Transceiver ICS(4169)

- HF-Schalter(9276)

- RF Shields(16401)

- HF-Receiver(1998)

- HF -Empfänger, Sender und Transceiver -Einheiten(2763)

- RF Power Divider/Splitter(1223)

- RF Power Controller ICs(86)

- HF-Modulatoren(710)

- HF-Mixer(2800)

- RF misc ICS und Module(3276)

- HF-Front-End (LNA + PA)(419)

- RF -Bewertungs- und Entwicklungskits, Boards(747)

- HF-gerichtete Kupplung(2718)

- RF Diplexer(1464)

- RF-Detektoren(412)

- RF-Demodulatoren(249)

- HF-Antennen(12319)

- HF-Verstärker(19651)

- Balun(1496)

- Dämpfungsglieder(4852)

-

Optoelektronik

Optoelektronik

- Optomechanisch(480)

- Leuchten(125)

- Laserdioden, Lasermodule - Laserlieferung, Laserfasern(345)

- Hene Lasersysteme(31)

- Hene Laserköpfe(27)

- Hintergrundbeleuchtung anzeigen(93)

- Xenon-Beleuchtung(387)

- Touchscreen-Overlays(453)

- Panel Indicators, Pilot Lights(75729)

- Optik-Remote-Phosphor-Lichtquelle(269)

- Optik-Reflektoren(665)

- Optik-leichte Rohre(5384)

- Optik-Objektive(4951)

- LEDs-Spacer, Unentschieden(2718)

- LEDs-Lamp-Ersetzungen(29718)

- LEDs - Leiterplattenindikatoren, Arrays, Lichtstäbe, Balkendiagramme(9083)

- LED-thermische Produkte(667)

- LED-Beleuchtung(64)

- LED-Beleuchtung-weiß(37580)

- LED-Beleuchtung-Farbe(4728)

- LED-Beleuchtung-Maiskolben, Motoren, Module(28735)

- LED-Anzeige-diskret(27601)

- Laserdioden, Module(1553)

- Lampen-Glühlampen, Neons(311004)

- Lampen-Kälte-Fluoreszenz (KKL) & UV(164)

- Wechselrichter(7728)

- Infrarot, UV, sichtbare Strahler(3871)

- Fiber Optics-Transmitter-Antrieb integriert(4085)

- Fiber Optics-Transmitter-diskrete(350)

- Fiber Optics-Transceiver Module(18758)

- Fiberoptik-Switches, Multiplexer, Demultiplexer(1387)

- Fiberoptik-Receiver(695)

- Fiberoptik-Dämpfung(654)

- Elektrolumineszenz(102)

- Display, Monitor-Interface Controller(98)

- Display-Module-Vakuum-Leuchtstofflampen (VFD)(249)

- Module anzeigen-LED Dot Matrix und Cluster(865)

- Display-Module-LED-Zeichen und numerische(5421)

- Display-Module-LCD, OLED, Graphic(4654)

- Display-Module-LCD, OLED-Zeichen und numerische(2202)

- Display-Blenden, Objektive(88)

- Adresse, Spezialität(458)

-

Sensoren, Wandler

Sensoren, Wandler

- Ultraschallempfänger, Sender - Industrial(115)

- Temperatursensoren - Thermostate - Mechanisch - Industrielles(3103)

- Temperatursensoren - Analog und digitaler Ausgang - Industrial(209)

- Näherungssensoren - Industrial(13611)

- Drucksensoren, Wandler - Industrie(26503)

- Optische Sensoren - Photonik - Zähler, Detektoren, SPCM (Einzelphotonzählmodul)(751)

- Optische Sensoren - Kameramodule(875)

- Magnetsensoren - Position, Nähe, Geschwindigkeit (Module) - Industrie(554)

- Kraftsensoren - Industrial(346)

- Flusssensoren - Industrielles(151)

- Float, Level Sensoren - Industrial(310)

- Encoder - Industrial(4980)

- Farbsensoren - Industrial(50)

- Berührungssensoren(100)

- Ultraschall-Receiver, Transmitter(2421)

- Temperatursensoren-Thermostat-Solid State(1096)

- Temperatursensoren-Thermostate-mechanisch(3397)

- Temperatursensoren - Thermoelemente, Temperatursonden(1921)

- Temperatursensoren - RTD (Widerstandstemperaturdetektor)(1525)

- Temperatursensoren-PTC-Thermistoren(2273)

- Temperatursensoren-ntc-thermistoren(13259)

- Temperatursensoren-Analog und Digital Output(3928)

- DMS(1399)

- Spezialisierte Sensoren(1861)

- Solarzellen(503)

- Schock-Sensoren(84)

- Sensor-Interface-Junction-Blöcke(2519)

- Sensor-Kabel-Baugruppen(22011)

- Proximity/Belegung Sensoren-fertige Einheiten(725)

- Näherungsschalter(2860)

- Drucksensoren, Wandler(11317)

- Positionssensoren - Winkel, lineare Positionsmessung(6022)

- Optische Sensoren-reflektierende-Logik-Ausgang(194)

- Optische Sensoren - reflektierend - analoge Ausgang(432)

- Optische Sensoren-Phototransistoren(1027)

- Optische Sensoren - Photointerrupter - Schlitztyp - Transistorausgang(1427)

- Optische Sensoren - Photointerrupter - Schlitztyp - Logikausgabe(1215)

- Optische Sensoren-Lichtschranke, Industrial(16763)

- Optische Sensoren-Photodioden(1543)

- Optische Sensoren-Foto-Detektoren-Remote Receiver(2605)

- Optische Sensoren-Foto-Detektoren-Logik-Ausgang(146)

- Optische Sensoren-Foto-Detektoren-CDs-Zellen(74)

- Optische Sensoren-Distanz-Messung(377)

- Optische Sensoren-Ambient Light, IR, UV Sensoren(1305)

- Multifunktions(558)

- Motion Sensors-Vibration(337)

- Motion Sensors-Tilt Schalter(67)

- Bewegungsmelder-optisch(719)

- Motion Sensors-Neigungssensoren(175)

- Motion Sensors-Imus (Trägheit-Maßeinheiten)(416)

- Motion Sensors-Kreisel(214)

- Motion Sensors-Beschleunigungsmesser(1911)

- Magnete-Sensor abgestimmt(119)

- Magnete-Multi Purpose(1965)

- Magnetische Sensoren-Schalter (Solid State)(3700)

- Magnetsensoren - Position, Nähe, Geschwindigkeit (Module)(5199)

- Magnetische Sensoren-linear, Kompass (ICS)(1247)

- Magnetsensoren - Kompass, Magnetfeld (Module)(35)

- LVDT -Wandler (linearer variabler Differentialtransformator)(204)

- IrDA Transceiver-Module(196)

- Bildsensor, Kamera(2235)

- Feuchtigkeit-Sensoren(1425)

- Gas-Sensoren(1217)

- Force Sensoren(188)

- Durchfluss-Sensoren(550)

- Float, Level Sensoren(1343)

- Encoder(6357)

- Staub-Sensoren(43)

- Aktuelle Wandler(3455)

- Color Sensoren(85)

- Verstärker(1905)

-

Anschlüsse, Verbindungen

Anschlüsse, Verbindungen

- USB, DVI, HDMI -Stecker(446)

- Festkörperbeleuchtungsstecker(555)

- Steckdosen für ICs, Transistoren(953)

- Steckbare Steckverbinder(1221)

- Photovoltaik (Solarpanel) Anschlüsse(136)

- Glasfaseranschlüsse(370)

- FFC, FPC (flache flexible) Anschlüsse(761)

- D-Sub, D-förmige Stecker(2887)

- Koaxialverbinder (RF)(2389)

- Rundanschlüsse(14162)

- Stromanbeter Blade Type(273)

- Stecker und Behälter(2597)

- USB, DVI, HDMI Stecker-Adapter(572)

- USB, DVI, HDMI -Stecker(4298)

- Klemmen-Wire to Board Steckverbinder(217)

- Klemmen-Draht-Steckverbinder(4322)

- Klemmen-Draht-Pin Stecker(328)

- Terminals-Revolver Steckverbinder(1273)

- Terminals-spezialisierte Steckverbinder(2042)

- Klemmen-Spaten Verbinder(3902)

- Klemmen-Löten/Stecker(345)

- Klemmen-Verschraubungen(745)

- Klemmen-Ring Steckverbinder(12596)

- Klemmen-rechteckige Steckverbinder(4747)

- Terminals - Schnellverbindungen, schnelle Trennungsanschlüsse(8514)

- Klemmen-PC PIN, Single Post Connectors(3776)

- Klemmen-PC-Pin-Buchsen, Sockel-Steckverbinder(5883)

- Klemmen-magnetische Draht-Steckverbinder(1653)

- Klemmen-Messer Steckverbinder(112)

- Klemmen-Gehäuse, Stiefel(2850)

- Klemmen-Folie Steckverbinder(108)

- Klemmen-Barrel, Bullet-Steckverbinder(1107)

- Klemmen-Adapter(137)

- Terminal-Streifen und Revolver-Boards(1159)

- Terminal Junction Systeme(2533)

- Anschlussblöcke-Draht an Bord(43615)

- Terminal Blocks-spezialisierte(3722)

- Terminal Blocks-Power Distribution(847)

- Anschlussblöcke-Panel Mount(1359)

- Terminal Blocks-Interface Module(1819)

- Anschlussblöcke-Kopfzeilen, Stecker und Buchsen(119920)

- Anschlussblöcke-DIN-Schiene, Kanal(9373)

- Anschlussblöcke-Kontakte(65)

- Anschlussblöcke-Barrier Blocks(47517)

- Anschlussblöcke-Adapter(1059)

- Solid State Lighting Verbinder-Kontakte(271)

- Festkörperbeleuchtungsstecker(1344)

- Buchsen für ICS, Transistoren-Adapter(275)

- Steckdosen für ICs, Transistoren(22148)

- Shunts, Jumper(907)

- Rechteckige Verbinder-Feder geladen(7721)

- Rechteckige Steckverbinder-Gehäuse(43023)

- Rechteckige Verbinder-Kopfzeilen, Spezial-PIN(6129)

- Rechteckige Anschlüsse - Header, Gefäße, weibliche Sockel(229601)

- Rechteckige Verbinder-Kopfzeilen, männliche Pins(543338)

- Rechteckige Anschlüsse - kostenloses Hängen, Panelhalterung(30142)

- Rechteckige Verbinder-Kontakte(10681)

- Rechteckige Anschlüsse - Board in, Direktdraht zum Board(2432)

- Rechteckige Verbinder-Adapter(475)

- Rechteckig - Brett zu Board -Steckern - Header, Behälter, weibliche Sockel(9)

- Rechteckig - Brett zu Board -Steckern - Header, männliche Stifte(2)

- Rechteckige Anschlüsse - Board -Abstandshalter, Stacker (Board zu Board)(238901)

- Rechteckige Anschlüsse - Arrays, Kantentyp, Mezzanin (Board zu Board)(37853)

- Stromanschluss-Eingänge, Steckdosen, Module(10310)

- Steckbare Steckverbinder(6049)

- Photovoltaik- (Solarpanel) Anschlüsse - Kontakte(77)

- Photovoltaik (Solarpanel) Anschlüsse(504)

- Modulare Steckverbinder-Verdrahtung Blöcke(99)

- Modulare Steckverbinder-Stecker(1674)

- Modulare Steckverbinder-Stecker Gehäuse(181)

- Modulare Steckverbinder-Buchsen mit magnetischen(10152)

- Modulare Steckverbinder-Buchsen(23416)

- Modulare Steckverbinder-Adapter(855)

- Memory Connectors-PC Cards-Adapter(21)

- Memory Connectors-PC Card Sockets(3299)

- Memory Connectors-Inline Modul Sockets(3390)

- LGH Steckverbinder(764)

- Keystone-Einsätze(2758)

- Keystone-Frontplatte, Frames(1926)

- Heavy Duty Steckverbinder-Einsätze, Module(4190)

- Schwerlastanschlüsse - Gehäuse, Kapuzen, Basen(17226)

- Heavy Duty Steckverbinder-Frames(523)

- Heavy Duty Steckverbinder-Kontakte(1832)

- Heavy Duty Steckverbinder-Baugruppen(671)

- LWL-Steckverbinder-Gehäuse(919)

- Glasfaser-Steckverbinder - Adapter(4455)

- LWL-Steckverbinder(3001)

- FFC, FPC (flache flexible) Steckverbinder - Gehäuse(652)

- FFC, FPC (flache flexible) Anschlüsse - Kontakte(202)

- FFC, FPC (flache flexible) Anschlüsse(18691)

- D-Sub, d-förmige Steckverbinder-Terminatoren(47)

- D-Sub, d-förmige Steckverbinder-Gehäuse(12238)

- D-Sub, d-förmige Steckverbinder-Kontakte(2714)

- D-Sub, D-förmige Steckverbinder-Rückenschalen, Kapuzen(5995)

- D-Sub, d-förmige Steckverbinder-Adapter(1304)

- D-Sub Steckverbinder(141346)

- D-förmige Steckverbinder-Centronics(8770)

- Kontakte, Frühling geladen und Druck(630)

- Kontakte-Multi Purpose(6196)

- Kontakte-"Leadframe"(122)

- Koaxial-Steckverbinder (RF)-Terminatoren(1231)

- Koaxial-Steckverbinder (RF)-Kontakte(480)

- Koaxial-Steckverbinder (RF)-Adapter(6386)

- Koaxialverbinder (RF)(25734)

- Rundsteckverbinder-Gehäuse(441226)

- Rundsteckverbinder-Kontakte(4737)

- Rundsteckverbinder-backschalen und Kabel-Klemmen(53692)

- Rundsteckverbinder-Adapter(8839)

- Rundanschlüsse(1196254)

- Card Edge Steckverbinder-Gehäuse(469)

- Karte Edge Verbinder-edgeboard Verbinder(672683)

- Card Edge Verbinder-Kontakte(325)

- Card Edge Verbinder-Adapter(73)

- Blade Type Power Steckverbinder-Gehäuse(837)

- Blade Type Power Connectors-Kontakte(393)

- Stromanbeter Blade Type(4163)

- Zwischen Serien-Adapter(649)

- Barrel-Stromanschluss(935)

- Barrel-Audio-Anschlüsse(2432)

- Barrel-Audio Adapter(92)

- Banana und Tip Steckverbinder-Buchsen, Stecker(1644)

- Banana and Tip Connectors-Binding Posts(239)

- Banana und Tip Steckverbinder-Adapter(75)

- Backplane Steckverbinder-spezialisiert(45586)

- Backplane Steckverbinder-Gehäuse(6863)

- Backplane Steckverbinder-Hard metrisch, Standard(6297)

- Backplane Steckverbinder-DIN 41612(9408)

- Backplane Steckverbinder-Kontakte(3583)

- Backplane Connectors-ARINC Einsätze(2357)

- Backplane Steckverbinder-ARINC(3789)

-

Widerstände

-

Kondensatoren

Kondensatoren

- Aluminium-Elektrolytkondensatoren(16817)

- Trimmer, Variable Kondensatoren(3151)

- Dünne Folien-Kondensatoren(3473)

- Tantal-Kondensatoren(136103)

- Tantal-Polymer-Kondensatoren(9778)

- Silizium-Kondensatoren(320)

- Niob Oxide Kondensatoren(330)

- Mica und PTFE Kondensatoren(9101)

- Folien-Kondensatoren(150406)

- Elektrische Doppelschichtkondensatoren (EDLC), Superkondensatoren(2782)

- Keramische Kondensatoren(833829)

- Kondensatoren-Netzwerke, Arrays(2383)

- Aluminium-Elektrolytkondensatoren(125325)

- Aluminium-Polymer-Kondensatoren(7544)

-

Transformatoren

-

Isolatoren

-

Kristalle, Oszillatoren, Resonatoren

-

Switches

Switches

- Verriegelungsschalter(2893)

- Emergency-Stop-Schalter (E-Stop)(1160)

- Kabelzugschalter(571)

- Toggle-Schalter(33608)

- Rändelrads Schalter(742)

- Schalter(14263)

- Snap-Aktion, Endschalter begrenzen(28077)

- Slide-Schalter(5166)

- Selector-Schalter(9720)

- Rotary Switches(13850)

- Rocker Schalter(53790)

- Drucktaste-Schalter-Hall-Effekt(127)

- Drucktaste Schalter(190826)

- Programmierbare Display-Switches(39)

- Navigations-Schalter, Joystick(1882)

- Magnetische, Reed-Schalter(1399)

- Keypad-Schalter(637)

- Keylock Schalter(3684)

- DIP Schalter(7747)

- Konfigurierbare Switch-Komponenten-Objektiv(1435)

- Konfigurierbare Schalter-Komponenten-Lichtquelle(1236)

- Konfigurierbare Switch-Komponenten-Contact Block(1401)

- Konfigurierbare Switch-Komponenten-Body(16077)

- Disconnect-Switch-Komponenten(2567)

-

Relais

Relais

- Sicherheitsrelais(1310)

- Reedrelais(1735)

- Hochfrequenz (RF) -Relais(1190)

- Schütze (Festkörper)(686)

- Schütze (elektromechanisch)(11952)

- Kfz-Relais(1881)

- Solid State Relais(10652)

- Signal-Relais, bis zu 2 Ampere(9149)

- Relay-Sockets(2075)

- Power Relays, über 2 Ampere(31604)

- E / A-Relaismodule(712)

- I/o-Relay-Module-Input(2)

- I/o-Relay-Modul-Racks(247)

Sprache auswählen

Aktuelle Sprache

Deutsch

- English

- Deutsch

- Italia

- Français

- 日本語

- 한국의

- русский

- Svenska

- Nederland

- español

- Português

- polski

- Suomi

- Gaeilge

- Slovenská

- Slovenija

- Čeština

- Melayu

- Magyarország

- Hrvatska

- Dansk

- românesc

- Indonesia

- Ελλάδα

- Български език

- Afrikaans

- IsiXhosa

- isiZulu

- lietuvių

- Maori

- Kongeriket

- Монголулс

- O'zbek

- Tiếng Việt

- हिंदी

- اردو

- Kurdî

- Català

- Bosna

- Euskera

- العربية

- فارسی

- Corsa

- Chicheŵa

- עִבְרִית

- Latviešu

- Hausa

- Беларусь

- አማርኛ

- Republika e Shqipërisë

- Eesti Vabariik

- íslenska

- မြန်မာ

- Македонски

- Lëtzebuergesch

- საქართველო

- Cambodia

- Pilipino

- Azərbaycan

- ພາສາລາວ

- বাংলা ভাষার

- پښتو

- malaɡasʲ

- Кыргыз тили

- Ayiti

- Қазақша

- Samoa

- සිංහල

- ภาษาไทย

- Україна

- Kiswahili

- Cрпски

- Galego

- नेपाली

- Sesotho

- Тоҷикӣ

- Türk dili

- ગુજરાતી

- ಕನ್ನಡkannaḍa

- मराठी

Verständnis der JK Flip-Flop-Konvertierung: Wahrheitstabellen, K-Maps und Anwendungen

Zeit: 2025/08/5

Durchsuchen: 4,692

Katalog

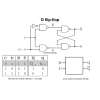

Abbildung 1. JK Flip-Flop

Was ist ein JK Flip-Flop?

Ein JK-Flip-Flop ist eine Art von Multivibrator, die in der digitalen Elektronik verwendet werden, um binäre Daten zu speichern und zu steuern.Es verfügt über zwei Eingänge, J (Set) und K (Reset) sowie ein Takteingang und einen Ausgang Q (und deren Komplement q ').Der Ausgangszustand des Flip-Flop ändert sich nur am ausgelösten Rand des Taktsignals (normalerweise steigend oder fallende Kante), abhängig von den Werten von J und K in diesem Moment.

Der JK Flip-Flop ist eine Verbesserung gegenüber dem SR-Flip-Flop (SET-Re-Reset), der unter einem unbestimmten Zustand leidet, wenn beide Eingaben hoch sind (1).Das JK -Design löst diese Mehrdeutigkeit durch Einführung eines Toggle -Modus auf, sodass der Ausgang die Zustände wechseln kann, wenn beide Eingänge 1 sind.

JK Flip-Flop Wahrheitstabelle:

|

J |

K |

Beschreibung |

Qnext |

|

0 |

0 |

Keine Änderung |

Q |

|

1 |

0 |

Satz |

1 |

|

0 |

1 |

Zurücksetzen |

0 |

|

1 |

1 |

Umschalten |

Q' |

• j = 0, k = 0: Die Ausgabe bleibt unverändert;Dies ist die Hold -Bedingung.

• j = 1, k = 0: Die Ausgabe ist auf 1 eingestellt.

• j = 0, k = 1: Die Ausgabe wird auf 0 zurückgesetzt.

• j = 1, k = 1: Der Ausgang umschalten (umdreht seinen Zustand auf jedem Taktpuls).

Warum JK Flip-Flops konvertieren?

Obwohl JK Flip-Flops aufgrund ihrer Fähigkeit, alle grundlegenden Speichervorgänge zu behandeln (Setzen, Zurücksetzen, Halten und Umschalten), sehr vielseitig sind, sind sie nicht immer die effizienteste Wahl für jedes digitale Design.In vielen Fällen kann das Konvertieren eines JK-Flip-Flop in einen anderen Flip-Flop-Typ wie D (Daten), T (Toggle) oder SR (SET-Re-Reset) zu einfacheren, optimierteren Schaltungen führen.

Jeder Flip-Flop-Typ verfügt über ein einzigartiges Verhalten, das für bestimmte Anwendungen geeignet ist.Beispielsweise sind D Flip-Flops ideal für die Datenspeicherung und -synchronisation.T Flip-Flops werden in den Zählern häufig verwendet.und SR Flip-Flops werden häufig in Kontrollsystemen verwendet, in denen explizite Set/Reset-Befehle erforderlich sind.Das Konvertieren von JK-Flip-Flops hilft, die Schaltung auf diese spezifischen Rollen zuzuordnen, ohne das gesamte System neu zu gestalten.

Vorteile der Umwandlung von JK Flip-Flops

• Reduziert die logische Komplexität: Vereinfacht die Schaltfläche Schaltplätze, indem zusätzliche Tore eliminiert werden, die erforderlich sind, um bestimmte Funktionen mithilfe der JK -Logik zu implementieren.

• Stromleitungen Debugging und Simulation: Einfacher zu testen und zu beheben, die einfachere Flip-Flop-Typen sowohl in Software-Simulation als auch in Hardware-Umgebungen beheben.

• Optimiert die Zeitleistung: Reduziert die Ausbreitungsverzögerungen und potenzielle Zeitprobleme, indem unnötige logische Übergänge minimiert werden.

• Verbessert die Modularität und Kompatibilität: Ermöglicht eine bessere Integration mit bereits bestehenden Modulen oder standardisierten digitalen Komponenten, für die möglicherweise spezifische Flip-Flop-Typen erforderlich sind.

Schritte zum Konvertieren von JK Flip-Flops

Schritt 1: Definieren Sie das Eingabeverpeilungsverhalten von Target Flip-Flop

Beginnen Sie mit, wie das Zielflip-Flop funktioniert.Beispielsweise überträgt ein D Flip-Flop seine Eingabe D direkt an die Ausgabe von Q an einer Taktkante, während ein T-Flip-Flop seine Ausgabe umschaltet, wenn t = 1. dieses Verhalten Sie hilft, es genau der JK-Logik zuzuordnen.

Schritt 2: Verweisen Sie auf die JK -Anregungstabelle

Die Anregungstabelle zeigt die erforderlichen J- und K -Eingangswerte, die erforderlich sind, um Übergänge vom aktuellen Zustand (QN) zum nächsten Zustand (qn+1) zu verursachen.Dies dient während der Konvertierung als Suchanleitung.

Schritt 3: Erstellen Sie eine Conversion -Wahrheitstabelle

Erstellen Sie eine Wahrheitstabelle, die den gegenwärtigen Zustand (QN) enthält, der im nächsten Zustand gewünscht wird (qN+1), die Zielflip-Flop-Eingabe (D, T oder SR) und die erforderlichen J- und K-Werte.Mit dieser Zuordnung können Sie die logische Beziehung zwischen dem Zielflip-Flop-Eingang und den Eingängen des JK Flip-Flop visualisieren.

Schritt 4: Verwenden Sie Karnaugh Maps (K-Maps), um logische Ausdrücke zu vereinfachen

Zeichnen Sie die abgeleiteten Werte für J und K aus Ihrer Konvertierungstabelle auf Karnaugh -Karten.K-Maps helfen dabei, die booleschen Ausdrücke zu minimieren, indem es benachbarte 1S-Bedingungen gruppiert, was zu einer einfacheren und effizienteren Logikimplementierung führt.

Schritt 5: Leiten Sie die erforderlichen J- und K -Eingangsgleichungen ab

Schreiben Sie basierend auf den vereinfachten K-MAP-Gruppierungen die booleschen Ausdrücke für J und K in Bezug auf die Zielflip-Flop-Eingabe und den aktuellen Zustand Q. Diese Gleichungen treiben das JK-Flip-Flop an, um sich wie der gewünschte Typ zu verhalten.

Schritt 6: Validieren Sie die Konvertierung

Bestätigen Sie Ihr Design, indem Sie die resultierende JK Flip-Flop-Logik gegen das Verhalten des Zielflip-Flops überprüfen.Sie können dies mit Wahrheitstabellen, Timing -Diagrammen oder digitalen Simulationswerkzeugen (z. B. logisim-, multisim- oder verilog -Testbengen) tun, um sicherzustellen, dass die Konvertierung logisch klug ist.

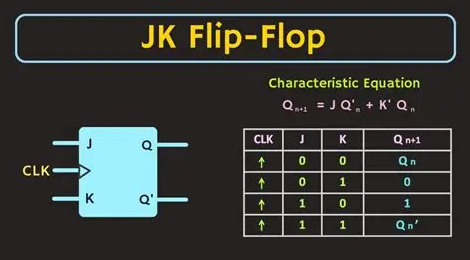

JK zu D Flip-Flop-Konvertierung

Abbildung 2. Jk zu D Flip-Flop-Umwandlung

Das D Flip-Flop, kurz für Daten oder Verzögerungsflip-Flop, ist eines der einfachsten und am häufigsten verwendeten sequentiellen Logikgeräte.Es erfasst den Wert des Eingangs D und überträgt ihn auf die Ausgangs -Q am auslösenden Rand der Uhr (normalerweise die steigende Kante).Sein definierendes Merkmal ist, dass der nächste Zustand der Ausgabe ausschließlich vom Wert von D abhängt, was ihn ideal für Datenspeicher, Register und synchroner Verriegelung macht.

Zielverhalten von D Flip-Flop:

• q Weiter = D.

Dies bedeutet, dass bei jedem Taktpuls der Ausgang einfach zu dem Eingang D in diesem Moment wird.

Um das Verhalten von D Flip-Flop mit einem JK-Flip-Flop zu implementieren, müssen wir die entsprechenden logischen Ausdrücke für J und k finden, die dazu führen, dass sich das JK Flip-Flop identisch verhalten, d. H. Sein Ausgangsausgang Q für den jeweiligen Taktzyklus aktualisieren.

Conversion -Wahrheitstabelle:

|

QT (gegenwärtiger Zustand) |

D (Zieleingabe) |

Qt+1 (nächster Zustand) |

J |

K |

|

0 |

0 |

0 |

0 |

X |

|

0 |

1 |

1 |

1 |

0 |

|

1 |

0 |

0 |

0 |

1 |

|

1 |

1 |

1 |

X |

0 |

• X Bezeichnet "egal", was bedeutet, dass die Eingabe entweder 0 oder 1 sein kann, ohne das Ergebnis zu beeinflussen.

• Die Tabelle entspricht den erwarteten Übergängen aus dem D Flip-Flop und bestimmt die entsprechenden J- und K-Eingänge, die für jeden Fall erforderlich sind.

Karnaugh -Karte Vereinfachung (optional)

Sie können optional Karnaugh Maps (K-Maps) verwenden, um die aus dieser Wahrheitstabelle abgeleiteten Booleschen logischen Ausdrücke zu vereinfachen.Die minimierte Logik führt in den folgenden Gleichungen:

Abgeleitete Logikgleichungen:

• j = d · q '

J wird nur dann geltend gemacht, wenn d = 1 und der Strom q = 0 (d. H. Eine "Set" -Simitus).

• k = q · d '

K wird nur dann geltend gemacht, wenn d = 0 und der Strom q = 1 (d. H. Eine "Reset" -Simate).

Diese Gleichungen stellen sicher, dass jeweils nur einer der J- oder K-Eingänge aktiv ist. Dies verhindert ein unbeabsichtigtes Umschalten und reproduziert das Verhalten eines D Flip-Flop genau.

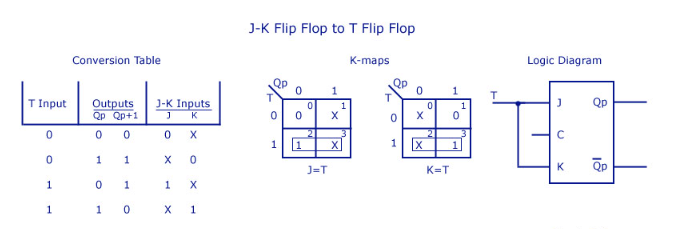

JK, um T-Flip-Flop-Konvertierung zu erreichen

Abbildung 3. JK, um T-Flip-Flop-Umwandlung zu erreichen

Der T Flip-Flop (Toggle Flip-Flop) ist eine vereinfachte Form des JK-Flip-Flop, der seinen Ausgangszustand nur dann ändert, wenn der Eingang t = 1 während einer Taktkante.Wenn t = 0, bleibt die Ausgabe unverändert.Dieses Verhalten lässt T-Flip-Flops ideal für die Implementierung von Binärzählern, Frequenzteilern und anderen Anwendungen, bei denen das Umschalten in jedem Taktzyklus benötigt wird.

Zielverhalten von T Flip-Flop:

• q Weiter = q ⊕ t

Mit anderen Worten:

• Wenn T = 0, Dann Qnächste = Q (Keine Änderung).

• Wenn T = 1, Dann Qnächste = Q ' (Umschalten).

Um dieses Verhalten mit einem JK-Flip-Flop zu replizieren, müssen wir die Logikwerte von J und k bestimmen, die den JK Flip-Flop umschalten, wenn t = 1, und seinen Zustand bei t = 0 gedrückt halten.

Conversion -Wahrheitstabelle:

|

QT (gegenwärtiger Zustand)

|

T (Zieleingabe) |

Qt+1 (nächster Zustand) |

J |

K |

|

0 |

0 |

0 |

0 |

X |

|

0 |

1 |

1 |

1 |

0 |

|

1 |

0 |

1 |

X |

0 |

|

1 |

1 |

0 |

0 |

1 |

• Die Tabelle zeigt die erforderlichen J- und K-Werte für das JK Flip-Flop, um sich wie ein T-Flip-Flop für jede Kombination von QT und T zu verhalten.

• X Zeigt "egal" -Werte an, die das Ergebnis nicht beeinflussen.

Abgeleitete Logikgleichungen:

Mit der Wahrheitstabelle oder Karnaugh -Karten (zur formellen Minimierung) kommen wir zu den einfachsten logischen Ausdrücken:

• j = t

• k = t

Beide Eingänge empfangen das gleiche Toggle Control Signal (t).Dieses Setup bewirkt, dass der JK Flip-Flop seine Ausgabe umschaltet, wenn T hoch (1) ist, und den aktuellen Zustand zu halten, wenn t niedrig ist (0), und das Verhalten von T Flip-Flop genau nachahmt.

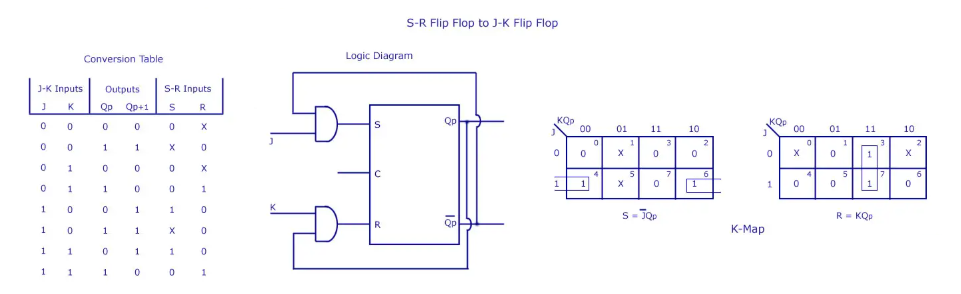

JK zu SR Flip-Flop-Umwandlung

Abbildung 4. JK zu SR Flip-Flop-Umwandlung

Das SR Flip-Flop (Set-Re-Reset Flip-Flop) ist eine der einfachsten Arten von herrlichen Geräten, die in der digitalen Elektronik verwendet werden.Es arbeitet mit zwei Steuereingängen: S (Set) und R (Reset).Diese Eingaben bestimmen direkt, ob der Ausgang Q auf 1 eingestellt ist, auf 0 zurückgesetzt oder konstant gehalten wird.Der SR-Flip-Flop wird häufig in grundlegenden Speicherspeichern, Steuerungssystemen und Zustandsmaschinen verwendet, bei denen explizite Set und Reset-Steuerung erforderlich sind.

Zielverhalten von SR Flip-Flop:

|

S |

R |

Qnext |

Beschreibung |

|

0 |

0 |

Q |

Keine Änderung |

|

0 |

1 |

0 |

Zurücksetzen |

|

1 |

0 |

1 |

Satz |

|

1 |

1 |

Undefiniert |

Ungültiger Zustand |

• S = 1, r = 0 → Ausgang ist auf 1 einstellen

• S = 0, r = 1 → Ausgang ist auf 0 zurücksetzen

• S = 0, r = 0 → Keine Änderung der Ausgabe (halten)

• S = 1, r = 1 → Ungültig Zustand (Konflikt zwischen Set und Reset)

Um das Verhalten eines SR-Flip-Flop mit einem JK-Flip-Flop zu replizieren, möchten wir die S- und R-Eingabebedingungen den entsprechenden J- und K-Werten abbilden.Das JK Flip-Flop muss das Set nachahmen, zurücksetzen und das Verhalten des SR-Flip-Flops halten und den ungültigen Zustand, in dem sowohl S als auch R hoch sind, sorgfältig vermieden.

Mapping Logic:

|

S |

R |

Gewünschte Aktion |

J |

K |

|

0 |

0 |

Halten |

0 |

0 |

|

0 |

1 |

Zurücksetzen (q = 0) |

0 |

1 |

|

1 |

0 |

Set (q = 1) |

1 |

0 |

|

1 |

1 |

Ungültig |

X |

X |

Basierend auf dieser Zuordnung ist die erforderliche Logik unkompliziert:

• j = s

• k = r

Diese direkte Aufgabe stellt sicher, dass:

• Wann S = 1 und r = 0, der Ausgang ist eingestellt (j = 1, k = 0)

• Wann S = 0 und r = 1, der Ausgang wird zurückgesetzt (j = 0, k = 1)

• Wann Sowohl s = 0 als auch r = 0, die Ausgabe hält (j = 0, k = 0)

Der S = 1, r = 1 Eingabekombination ist nicht erlaubt In SR Flip-Flops führt es zu einem undefinierten oder instabilen Zustand.Während der JK Flip-Flop selbst umgehen kann J = 1 und k = 1 Durch das Umschalten der Ausgabe dieses Verhalten ist nicht kompatibel mit SR -Logik.Bei der Emulation eines SR-Flip-Flops mit einer JK-Konfiguration müssen Sie daher die Eingangskonditionierungslogik (z. B. mit Gates oder Softwareprüfungen) implementieren, um zu verhindern, dass S und R gleichzeitig hoch sind.

JK Flip-Flop-Anregungstabelle

Die Anregungstabelle für ein JK Flip-Flop hilft bei der Gestaltung und Umwandlung von sequentiellen Schaltungen.Im Gegensatz zu einer Wahrheitstabelle, die die Ausgabe basierend auf aktuellen Eingängen zeigt, funktioniert die Anregungstabelle umgekehrt: Bestimmt die erforderlichen J- und K -Eingänge, die für den Übergang von einem gegenwärtigen Zustand (QT) in einen nächsten Zustand (QT+1) erforderlich sind.

Dies ist besonders nützlich, wenn JK-Flip-Flops in andere Typen (z. B. D, T oder SR) oder das Entwerfen von Finite-Status-Maschinen (FSMs) umgewandelt werden, wobei die gewünschten Zustandsübergänge bekannt sind und die Eingabebedingungen abgeleitet werden müssen.

JK Flip-Flop-Anregungstabelle:

|

QT |

Qt+1 |

J |

K |

|

0 |

0 |

0 |

X |

|

0 |

1 |

1 |

0 |

|

1 |

0 |

0 |

1 |

|

1 |

1 |

X |

0 |

Legende:

• QT: Aktueller Zustand der Ausgabe Q.

• Qt+1: Gewünschter nächster Staat.

• J und K: Erforderliche Eingaben, um den Übergang zu erreichen.

• X: "Egal" -Sbund - entweder 0 oder 1 funktionieren, ohne das Ergebnis zu beeinflussen.

So interpretieren Sie die Tabelle:

• QT= 0 → qt+1= 0: Haltenzustand → j = 0 (kein Satz benötigt), k = x (irrelevant).

• QT= 0 → qt+1= 1: Setzen Sie den Zustand → j = 1, k = 0.

• QT= 1 → qt+1= 0: RESET STATION → J = 0, K = 1.

• QT= 1 → qt+1= 1: Zustand halten → j = x, k = 0.

Rassenbedingung verhindern

Eine der potenziellen Herausforderungen bei der Verwendung von JK-Flip-Flops, insbesondere der ausgestrahlten Stufe, ist die Rennerkrankung.Dieses Problem tritt auf, wenn beide Eingänge j und k auf 1 eingestellt sind und der Taktpuls für eine Dauer lang genug bleibt (oder niedrig, abhängig von der Auslösung), damit der Ausgang q wiederholt innerhalb des gleichen Taktzyklus umschaltet.Infolgedessen wird der Ausgangszustand unvorhersehbar, was zu schwerwiegenden Fehlern in synchronen digitalen Systemen führen kann.

Ursachen für einen Rennerkrankung

In einem auf Level ausgelösten JK Flip-Flop:

• Wann J = k = 1Der Flip-Flop ist im Umschaltmodus.

• Wenn die Taktimpulsbreite länger ist als die Ausbreitungsverzögerung des Flip-Flop, schaltet der Ausgang während des Taktsignals kontinuierlich um, anstatt nur einmal umzuschalten.

• Diese schnelle, unkontrollierte Schaltung kann zu Störungen, unzuverlässigen Daten und falschen Statusübergängen in aufeinanderfolgenden Schaltungen wie Zählern oder Zustandsmaschinen führen.

Techniken zur Verhinderung des Rennstalls

Um nur einen gültigen Ausgangsübergang pro Taktzyklus zu gewährleisten, können Sie mehrere bewährte Methoden verwenden:

• Verwenden Sie die von Kanten ausgelöste JK Flip-Flops: Das Schalten von ausgeströschten auf kandentlich ausgelöste Flip-Flops-Grenzwerte Die Ausgangsänderungen in einen einzelnen Augenblick, entweder die steigende oder fallende Kante der Uhr.Dies beseitigt effektiv das Rennproblem, da der Flip-Flop nur einmal pro Taktpuls reagiert.

• Wenden Sie eine Master-Slave JK Flip-Flop-Konfiguration an: Dieses Setup verwendet zwei JK-Flip-Flops in Serien: Der Master erfasst Eingabedaten während der aktiven Phase der Uhr, während der Slave die Ausgabe während der inaktiven Phase aktualisiert.Diese inszenierte Reaktion stellt sicher, dass sich die endgültige Ausgangszyklus auch dann nur einmal pro Taktzyklus ändert, wodurch mehrere Übergänge verhindert werden.

• Verkürzen Sie die Taktpulsbreite: Durch die Reduzierung der Dauer des Taktpulses stellt er sicher, dass er kürzer ist als die Ausbreitungsverzögerung des Flip-Flop.Dies verhindert, dass die Ausgabe mehr als einmal umschaltet, selbst in ausgelösterten Konfigurationen.Diese Methode kann jedoch durch die minimalen Anforderungen an die Impulsbreite anderer Komponenten begrenzt werden.

Anwendungen von JK Flip-Flop-Konvertierungen

Bei der Auswahl des entsprechenden Flip-Flop-Designs ist im digitalen Systemdesign der Schlüssel zum Erreichen eines effizienten, modularen und vorhersehbaren Verhaltens.Obwohl JK Flip-Flops vielseitig sind, kann es dazu beitragen, die Logik zu rationalisieren, die Komplexität der Hardware zu verringern und die funktionale Klarheit in verschiedenen Anwendungen zu verbessern.

Durch das Verständnis der Art der Aufgabe, unabhängig davon, ob sie das Zählen, Speichern von Daten oder die Priorisierung von Signalen beinhalten, können Sie JK Flip-Flops auf die am besten geeignete Konfiguration zuordnen.Dies verbessert nicht nur die Systemleistung, sondern vereinfacht auch Debugging, Simulation und Zeitanalyse.

• Binäre Zähler (JK → T): T Flip-Flops Schalten Sie jeden Taktimpuls um, wodurch sie ideal für Ripple- oder Synchronzähler, wo jeder Flip-Flop eine binäre Ziffer darstellt.

• Serielle Datenspeicherung (JK → D): D Flip-Flops übergeben Eingangsdaten an der Taktrante an die Ausgabe und stellen Sie sicher, dass saubere Datenverriegelung und -verbreitung in Schaltregistern oder Datenpipelines festgelegt werden.

• Priority Control Logic (JK → SR): SR Flip-Flops bieten eindeutige Set- und Zurücksetzen von Steuerelementen, wodurch sie für Systeme mit manuellen Überschreibungen, staatlichbasierten Steuerung oder Interrupt-Logik geeignet sind.

• Frequenzteilung (JK → T): Da ein T-Flip-Flop seinen Ausgang auf jedem Taktimpuls umschaltet, teilt es die Frequenz auf natürliche Weise durch 2, was in der Taktivitäts- und Wellenformgenerierung nützlich ist.

Abschluss

JK Flip-Flops bieten eine flexible Funktionalität, aber das Umwandeln in D, T oder SR Flip-Flops kann Ihre digitalen Designs für bestimmte Aufgaben wie Zählen, Datenspeicherung oder Steuerlogik optimieren.Wenn Sie das Verhalten jedes Flip-Flop-Verhaltens verstehen und systematische Conversion-Techniken anwenden, indem Sie Wahrheitstabellen, Anregungstabellen und logische Vereinfachung verwenden, können Sie effizientere, modularere und zuverlässigere Systeme erstellen.Unabhängig davon, ob Sie an Zähler, Registern oder Kontrolleinheiten arbeiten, können Sie JK Flip-Flop-Conversions beherrschen, um intelligentere, anpassungsfähigere digitale Schaltkreise zu entwerfen.

Häufig gestellte Fragen [FAQ]

1. Kann ein JK Flip-Flop andere Flip-Flop-Typen in einer digitalen Schaltung ersetzen?

Ein JK Flip-Flop kann D, T oder SR Flip-Flops mit geeigneter Logik an seinen Eingängen emulieren.Für eine optimale Geschwindigkeit und Einfachheit ist die direkte Verwendung des Zielflip-Flop jedoch häufig besser in leistungsstarken oder ressourcenbegrenzten Designs.

2. Was sind die realen Anwendungsfälle für JK, um T Flip-Flop-Umwandlung zu erhalten?

JK zu T -Umwandlungen sind bei Frequenzteilern, Binärzählern und Wellenformgeneratoren üblich, wobei jede Anwendung in jedem Taktzyklus ohne komplexe Eingangskonditionierung eine Umschaltfunktion benötigt.

3. Warum ist die Vereinigung von Karnaugh Map bei JK Flip-Flop-Umwandlung wichtig?

Karnaugh Maps reduzieren die Boolesche Logik, die für J- und K -Eingänge während der Umwandlung benötigt wird, die Anzahl der Gate und die Verbesserung der Schaltungsgeschwindigkeit, der Stromversorgung und der Zuverlässigkeit.

4. Wie verhindern Sie ungültige Eingabeszustände bei der Emulation von SR-Flip-Flops mit JK-Flip-Flops?

Verwenden Sie externe Logik -Gates oder bedingte Logik, um die gleichzeitige S = 1 und r = 1 Eingänge zu blockieren.Dies verhindert ein definiertes Verhalten in der SR-Mode-Emulation und sorgt für eine stabile Ausgabe.

5. Ist es besser, JK Flip-Flops umzuwandeln oder die Schaltung mit nativen D/T/SR-Flip-Flops neu zu gestalten?

Für neue Designs bieten native Flip-Flops Einfachheit und Geschwindigkeit.Die JK-Konvertierung ist ideal für die Änderung vorhandener Systeme oder wenn nur JK-Flip-Flops in Hardware verfügbar sind.

Verwandter Artikel

-

Jul 31 2025Welche Größe Draht für einen 50 -Ampere -Brecher?

Bei der Installation eines 50-Amp-Leistungsschalters geht es bei der Auswahl der richtigen Drahtgröße nicht nur darum, die grundlegenden elektrische... -

Aug 11 2025Vollständige Anleitung für D Flip-Flop: Arbeit, Konvertierung und Designtipps

Dieser Artikel erkennt, was D Flip-Flop ist, wie es funktioniert, wie er funktioniert, seine verschiedenen Typen, Wahrheitstabellenverhalten und wie e...

Verwandte -Produkte

04023A620GAT2A

CAP CER 62PF 25V NP0 0402

08051U100JAT2A

CAP CER 10PF 100V C0G/NP0 0805

TAJT685M006SNJ

CAP TANT 6.8UF 20% 6.3V 1411

NTD5406NT4G

MOSFET N-CH 40V 12.2A/70A DPAK

IRLP3034PBF

MOSFET N-CH 40V 195A TO247AC

PCM1720E

IC DAC/AUDIO 24BIT 96K 20SSOP

MAX5971AETI+

IC POE CNTRL 1 CHANNEL 28TQFN

TM4C123BE6PZIR

IC MCU 32BIT 128KB FLASH 100LQFP

MM74HC373MTCX

BUS DRIVER, HC/UH SERIES, 1-FUNC

BTS5236-2EK

BTS5236-2EK INFINEO

BD82P55-QMPA

INTEL BGA

VSC7216UI-02

VITESSE 256BGA

KS6M7U3805WBP

ON/NORTEL BGA