Alle Kategorien

-

Integrierte schaltkreise (ICS)

Integrierte schaltkreise (ICS)

- Schnittstelle - Sensor, kapazitive Berührung(642)

- Spezialisierte ICS(12302)

- PMIC-Spannungsregler-besonderer Zweck(5644)

- PMIC-Spannungsregler-lineare Regler(793)

- PMIC-Spannungsregler-linear + Switching(1829)

- PMIC-Spannungsregler-linear(70981)

- PMIC-Spannungsregler-DC DC Switching Regulators(39569)

- PMIC-Regler-DC-DC-Switching-Controller(13507)

- PMIC-Spannungs-Referenz(9453)

- PMIC-v/f und f/v-Wandler(145)

- PMIC-Thermal Management(592)

- PMIC-Supervisor(47946)

- PMIC-RMS bis DC-Wandler(170)

- PMIC-Netzteil-Controller, Monitore(2104)

- PMIC-Power over Ethernet (PoE) Controller(1008)

- PMIC-Power Management-spezialisierte(7722)

- PMIC-Netzschalter, Treiber laden(7706)

- PMIC-PFC (Power Factor Correction)(1222)

- PMIC oder Steuerungen, ideale Dioden(705)

- PMIC-Motor-Treiber, Regler(4712)

- PMIC-Beleuchtung, Ballast-Regler(560)

- PMIC-LED-Treiber(7282)

- PMIC-Laser-Treiber(573)

- PMIC-Hot-Swap-Controller(2816)

- PMIC-Gate-Treiber(7083)

- PMIC-voll, Half-Bridge-Treiber(1342)

- PMIC-Energy Messung(654)

- PMIC-Display-Treiber(1435)

- PMIC-derzeitige Regulierung/Management(1481)

- PMIC-Batterie-Management(5553)

- PMIC-Ladegeräte(3831)

- PMIC-AC DC Konverter, Offline Schalter(4905)

- Memory-Controller(358)

- Memory-Konfigurations-Proms für FPGAs(639)

- Speicher-Akkus(13)

- Erinnerung(65694)

- Logic-universelle Bus-Funktionen(706)

- Logic-Übersetzer, Level-Shifter(2854)

- Logik-Specialty Logic(1870)

- Logik-Signal-Schalter, Multiplexer, Decoder(9420)

- Logic-Shift-Register(2665)

- Logic-Parity Generatoren und Checkers(335)

- Logic-multivibratoren(831)

- Logik-Latches(3658)

- Logik - Tore und Wechselrichter - Multifunktion, konfigurierbar(1687)

- Logik-Tore und Wechselrichter(16453)

- Logic-Flip Flops(7780)

- Logik-FIFOs Speicher(4240)

- Logik-Zähler, Trennlinien(3456)

- Logik-Vergleichsoperator(592)

- Logik-Puffer, Treiber, Receiver, Transceiver(17835)

- Linear-Video-Verarbeitung(2909)

- Linear-Vergleichsoperator(5084)

- Linear-analoge Multiplikatoren, Trennwände(263)

- Linear-Verstärker-Video Amps und Module(1905)

- Linear-Verstärker-Spezial-Zweck(1856)

- Linear - Verstärker - Instrumentierung, OP -Verstärker, Pufferverstärker(34236)

- Linear-Verstärker-Audio(4567)

- Interface-Voice Record und Playback(556)

- Schnittstelle - UARTs (Universal Asynchronous Receivers -Sender)(1237)

- Schnittstelle-Telecom(4467)

- Interface-spezialisierte(4833)

- Interface-Signal Terminatoren(333)

- Interface-Signal-Puffer, Repeater, Splitter(1449)

- Interface-Serializer, Deserializer(1480)

- Schnittstellen-Sensor und Detektor-Interfaces(1524)

- Interface-Module(169)

- Interface-Modems-ICS und Module(407)

- Interface-e/a-Expander(1136)

- Interface-Filter-aktiv(1226)

- Interface-Encoder, Decoder, Konverter(714)

- Interface-Treiber, Receiver, Transceiver(20755)

- Interface-Direct Digital Synthesis (DDS)(117)

- Interface-Controller(3628)

- Interface-Codecs(1676)

- Schnittstelle - Analoge Switches, Multiplexer, Demultiplexer(12567)

- Schnittstelle-analoge Schalter-spezieller Zweck(2533)

- Embedded-System on Chip (SoC)(4496)

- Embedded-PLDs (programmierbare Logik-Vorrichtung)(971)

- Embedded-Mikroprozessoren(10083)

- Embedded-Mikrocontroller-anwendungsspezifische(2275)

- Embedded-Mikrocontroller(99285)

- Eingebettet - Mikrocontroller, Mikroprozessor, FPGA -Module(1527)

- Eingebettet - FPGAs (Feldprogrammiergate -Array) mit Mikrocontrollern(81)

- Embedded-FPGAs (Field Programmable Gate Array)(27747)

- Embedded-DSP (Digital Signal Processors)(4081)

- Eingebettet - CPLDs (komplexe programmierbare Logikgeräte)(5187)

- Datenerfassung-Touch Screen Controller(1210)

- Datenerfassung-Digital to Analog Converter (DAC)(14419)

- Datenerfassung-digitale Potentiometer(6250)

- Datenerfassung-analog zu Digital Converters (ADC)(17776)

- Datenerfassung-analoges Frontend (AFE)(787)

- Datenerfassung-MDE/DACs-spezieller Zweck(3043)

- Clock/Timing-Uhren in Echtzeit(2446)

- Uhr/Timing - programmierbare Timer und Oszillatoren(23469)

- Clock/Timing-IC-Akkus(4)

- Takt/Timing-Delay Lines(1049)

- Uhr/Timing - Uhrengeneratoren, PLLS, Frequenzsynthesizer(32775)

- Clock/Timing-Clock Puffer, Treiber(4568)

- Clock/Timing-anwendungsspezifische(8652)

- Audio Spezial-Zweck(1564)

-

Diskrete Halbleiter-Produkte

Diskrete Halbleiter-Produkte

- Aktuelle Regulierung - Dioden, Transistoren(1090)

- Transistoren-besonderer Zweck(226)

- Transistoren-programmierbare Unijunction(48)

- Transistoren-jfets(1558)

- Transistoren-IGBTs-Einzel(4799)

- Transistoren-IGBTs-Module(63420)

- Transistoren-IGBTs-Arrays(26)

- Transistoren-FETs, MOSFETs-Einzel(48330)

- Transistoren-FETs, MOSFETs-RF(4903)

- Transistoren-FETs, MOSFETs-Arrays(6641)

- Transistoren-Bipolar (BJT)-einzeln, Pre-biased(4539)

- Transistoren-Bipolar (BJT)-Einzel(25800)

- Transistoren-Bipolar (BJT)-RF(2087)

- Transistoren-bipolare (BJT)-Arrays, Pre-biased(2115)

- Transistoren-bipolare (BJT)-Arrays(2310)

- Thyristor-triacs(4044)

- Thyristoren-SCRs-Module(3967)

- Thyristoren-SCRs(5436)

- Thyristoren-diacs, sidacs(319)

- Power Driver Module(1627)

- Dioden-zenerdioden-Einzel(87483)

- Dioden-zenerdioden-Arrays(2619)

- Dioden - variable Kapazität (Varik, Varaktoren)(1200)

- Dioden-RF(2753)

- Dioden-Gleichrichter-Einzel(67528)

- Dioden-Gleichrichter-Arrays(20581)

- Dioden-Brücke-Gleichrichter(11700)

-

RF/if und RFID

RF/if und RFID

- SIM -Karten für Abonnenten -Identifikationsmodul (SIM)(77)

- RF -Zirkulatoren und Isolatoren(1742)

- RFID, RF-Zugang, Monitoring-ICS(1550)

- RFID Transponder, Tags(747)

- RFID Lesegeräte(464)

- RFID -Bewertungs- und Entwicklungskits, Boards(30)

- RFID Antennen(329)

- RFI und EMI - Abschirm- und Absorbungsmaterialien(6444)

- HF und EMI-Kontakte, Fingerstock und Dichtungen(7497)

- RF Transmitter(668)

- RF Transceiver Module(6900)

- RF-Transceiver ICS(4169)

- HF-Schalter(9276)

- RF Shields(16401)

- HF-Receiver(1998)

- HF -Empfänger, Sender und Transceiver -Einheiten(2763)

- RF Power Divider/Splitter(1223)

- RF Power Controller ICs(86)

- HF-Modulatoren(710)

- HF-Mixer(2800)

- RF misc ICS und Module(3276)

- HF-Front-End (LNA + PA)(419)

- RF -Bewertungs- und Entwicklungskits, Boards(747)

- HF-gerichtete Kupplung(2718)

- RF Diplexer(1464)

- RF-Detektoren(412)

- RF-Demodulatoren(249)

- HF-Antennen(12319)

- HF-Verstärker(19651)

- Balun(1496)

- Dämpfungsglieder(4852)

-

Optoelektronik

Optoelektronik

- Optomechanisch(480)

- Leuchten(125)

- Laserdioden, Lasermodule - Laserlieferung, Laserfasern(345)

- Hene Lasersysteme(31)

- Hene Laserköpfe(27)

- Hintergrundbeleuchtung anzeigen(93)

- Xenon-Beleuchtung(387)

- Touchscreen-Overlays(453)

- Panel Indicators, Pilot Lights(75729)

- Optik-Remote-Phosphor-Lichtquelle(269)

- Optik-Reflektoren(665)

- Optik-leichte Rohre(5384)

- Optik-Objektive(4951)

- LEDs-Spacer, Unentschieden(2718)

- LEDs-Lamp-Ersetzungen(29718)

- LEDs - Leiterplattenindikatoren, Arrays, Lichtstäbe, Balkendiagramme(9083)

- LED-thermische Produkte(667)

- LED-Beleuchtung(64)

- LED-Beleuchtung-weiß(37580)

- LED-Beleuchtung-Farbe(4728)

- LED-Beleuchtung-Maiskolben, Motoren, Module(28735)

- LED-Anzeige-diskret(27601)

- Laserdioden, Module(1553)

- Lampen-Glühlampen, Neons(311004)

- Lampen-Kälte-Fluoreszenz (KKL) & UV(164)

- Wechselrichter(7728)

- Infrarot, UV, sichtbare Strahler(3871)

- Fiber Optics-Transmitter-Antrieb integriert(4085)

- Fiber Optics-Transmitter-diskrete(350)

- Fiber Optics-Transceiver Module(18758)

- Fiberoptik-Switches, Multiplexer, Demultiplexer(1387)

- Fiberoptik-Receiver(695)

- Fiberoptik-Dämpfung(654)

- Elektrolumineszenz(102)

- Display, Monitor-Interface Controller(98)

- Display-Module-Vakuum-Leuchtstofflampen (VFD)(249)

- Module anzeigen-LED Dot Matrix und Cluster(865)

- Display-Module-LED-Zeichen und numerische(5421)

- Display-Module-LCD, OLED, Graphic(4654)

- Display-Module-LCD, OLED-Zeichen und numerische(2202)

- Display-Blenden, Objektive(88)

- Adresse, Spezialität(458)

-

Sensoren, Wandler

Sensoren, Wandler

- Ultraschallempfänger, Sender - Industrial(115)

- Temperatursensoren - Thermostate - Mechanisch - Industrielles(3103)

- Temperatursensoren - Analog und digitaler Ausgang - Industrial(209)

- Näherungssensoren - Industrial(13611)

- Drucksensoren, Wandler - Industrie(26503)

- Optische Sensoren - Photonik - Zähler, Detektoren, SPCM (Einzelphotonzählmodul)(751)

- Optische Sensoren - Kameramodule(875)

- Magnetsensoren - Position, Nähe, Geschwindigkeit (Module) - Industrie(554)

- Kraftsensoren - Industrial(346)

- Flusssensoren - Industrielles(151)

- Float, Level Sensoren - Industrial(310)

- Encoder - Industrial(4980)

- Farbsensoren - Industrial(50)

- Berührungssensoren(100)

- Ultraschall-Receiver, Transmitter(2421)

- Temperatursensoren-Thermostat-Solid State(1096)

- Temperatursensoren-Thermostate-mechanisch(3397)

- Temperatursensoren - Thermoelemente, Temperatursonden(1921)

- Temperatursensoren - RTD (Widerstandstemperaturdetektor)(1525)

- Temperatursensoren-PTC-Thermistoren(2273)

- Temperatursensoren-ntc-thermistoren(13259)

- Temperatursensoren-Analog und Digital Output(3928)

- DMS(1399)

- Spezialisierte Sensoren(1861)

- Solarzellen(503)

- Schock-Sensoren(84)

- Sensor-Interface-Junction-Blöcke(2519)

- Sensor-Kabel-Baugruppen(22011)

- Proximity/Belegung Sensoren-fertige Einheiten(725)

- Näherungsschalter(2860)

- Drucksensoren, Wandler(11317)

- Positionssensoren - Winkel, lineare Positionsmessung(6022)

- Optische Sensoren-reflektierende-Logik-Ausgang(194)

- Optische Sensoren - reflektierend - analoge Ausgang(432)

- Optische Sensoren-Phototransistoren(1027)

- Optische Sensoren - Photointerrupter - Schlitztyp - Transistorausgang(1427)

- Optische Sensoren - Photointerrupter - Schlitztyp - Logikausgabe(1215)

- Optische Sensoren-Lichtschranke, Industrial(16763)

- Optische Sensoren-Photodioden(1543)

- Optische Sensoren-Foto-Detektoren-Remote Receiver(2605)

- Optische Sensoren-Foto-Detektoren-Logik-Ausgang(146)

- Optische Sensoren-Foto-Detektoren-CDs-Zellen(74)

- Optische Sensoren-Distanz-Messung(377)

- Optische Sensoren-Ambient Light, IR, UV Sensoren(1305)

- Multifunktions(558)

- Motion Sensors-Vibration(337)

- Motion Sensors-Tilt Schalter(67)

- Bewegungsmelder-optisch(719)

- Motion Sensors-Neigungssensoren(175)

- Motion Sensors-Imus (Trägheit-Maßeinheiten)(416)

- Motion Sensors-Kreisel(214)

- Motion Sensors-Beschleunigungsmesser(1911)

- Magnete-Sensor abgestimmt(119)

- Magnete-Multi Purpose(1965)

- Magnetische Sensoren-Schalter (Solid State)(3700)

- Magnetsensoren - Position, Nähe, Geschwindigkeit (Module)(5199)

- Magnetische Sensoren-linear, Kompass (ICS)(1247)

- Magnetsensoren - Kompass, Magnetfeld (Module)(35)

- LVDT -Wandler (linearer variabler Differentialtransformator)(204)

- IrDA Transceiver-Module(196)

- Bildsensor, Kamera(2235)

- Feuchtigkeit-Sensoren(1425)

- Gas-Sensoren(1217)

- Force Sensoren(188)

- Durchfluss-Sensoren(550)

- Float, Level Sensoren(1343)

- Encoder(6357)

- Staub-Sensoren(43)

- Aktuelle Wandler(3455)

- Color Sensoren(85)

- Verstärker(1905)

-

Anschlüsse, Verbindungen

Anschlüsse, Verbindungen

- USB, DVI, HDMI -Stecker(446)

- Festkörperbeleuchtungsstecker(555)

- Steckdosen für ICs, Transistoren(953)

- Steckbare Steckverbinder(1221)

- Photovoltaik (Solarpanel) Anschlüsse(136)

- Glasfaseranschlüsse(370)

- FFC, FPC (flache flexible) Anschlüsse(761)

- D-Sub, D-förmige Stecker(2887)

- Koaxialverbinder (RF)(2389)

- Rundanschlüsse(14162)

- Stromanbeter Blade Type(273)

- Stecker und Behälter(2597)

- USB, DVI, HDMI Stecker-Adapter(572)

- USB, DVI, HDMI -Stecker(4298)

- Klemmen-Wire to Board Steckverbinder(217)

- Klemmen-Draht-Steckverbinder(4322)

- Klemmen-Draht-Pin Stecker(328)

- Terminals-Revolver Steckverbinder(1273)

- Terminals-spezialisierte Steckverbinder(2042)

- Klemmen-Spaten Verbinder(3902)

- Klemmen-Löten/Stecker(345)

- Klemmen-Verschraubungen(745)

- Klemmen-Ring Steckverbinder(12596)

- Klemmen-rechteckige Steckverbinder(4747)

- Terminals - Schnellverbindungen, schnelle Trennungsanschlüsse(8514)

- Klemmen-PC PIN, Single Post Connectors(3776)

- Klemmen-PC-Pin-Buchsen, Sockel-Steckverbinder(5883)

- Klemmen-magnetische Draht-Steckverbinder(1653)

- Klemmen-Messer Steckverbinder(112)

- Klemmen-Gehäuse, Stiefel(2850)

- Klemmen-Folie Steckverbinder(108)

- Klemmen-Barrel, Bullet-Steckverbinder(1107)

- Klemmen-Adapter(137)

- Terminal-Streifen und Revolver-Boards(1159)

- Terminal Junction Systeme(2533)

- Anschlussblöcke-Draht an Bord(43615)

- Terminal Blocks-spezialisierte(3722)

- Terminal Blocks-Power Distribution(847)

- Anschlussblöcke-Panel Mount(1359)

- Terminal Blocks-Interface Module(1819)

- Anschlussblöcke-Kopfzeilen, Stecker und Buchsen(119920)

- Anschlussblöcke-DIN-Schiene, Kanal(9373)

- Anschlussblöcke-Kontakte(65)

- Anschlussblöcke-Barrier Blocks(47517)

- Anschlussblöcke-Adapter(1059)

- Solid State Lighting Verbinder-Kontakte(271)

- Festkörperbeleuchtungsstecker(1344)

- Buchsen für ICS, Transistoren-Adapter(275)

- Steckdosen für ICs, Transistoren(22148)

- Shunts, Jumper(907)

- Rechteckige Verbinder-Feder geladen(7721)

- Rechteckige Steckverbinder-Gehäuse(43023)

- Rechteckige Verbinder-Kopfzeilen, Spezial-PIN(6129)

- Rechteckige Anschlüsse - Header, Gefäße, weibliche Sockel(229601)

- Rechteckige Verbinder-Kopfzeilen, männliche Pins(543338)

- Rechteckige Anschlüsse - kostenloses Hängen, Panelhalterung(30142)

- Rechteckige Verbinder-Kontakte(10681)

- Rechteckige Anschlüsse - Board in, Direktdraht zum Board(2432)

- Rechteckige Verbinder-Adapter(475)

- Rechteckig - Brett zu Board -Steckern - Header, Behälter, weibliche Sockel(9)

- Rechteckig - Brett zu Board -Steckern - Header, männliche Stifte(2)

- Rechteckige Anschlüsse - Board -Abstandshalter, Stacker (Board zu Board)(238901)

- Rechteckige Anschlüsse - Arrays, Kantentyp, Mezzanin (Board zu Board)(37853)

- Stromanschluss-Eingänge, Steckdosen, Module(10310)

- Steckbare Steckverbinder(6049)

- Photovoltaik- (Solarpanel) Anschlüsse - Kontakte(77)

- Photovoltaik (Solarpanel) Anschlüsse(504)

- Modulare Steckverbinder-Verdrahtung Blöcke(99)

- Modulare Steckverbinder-Stecker(1674)

- Modulare Steckverbinder-Stecker Gehäuse(181)

- Modulare Steckverbinder-Buchsen mit magnetischen(10152)

- Modulare Steckverbinder-Buchsen(23416)

- Modulare Steckverbinder-Adapter(855)

- Memory Connectors-PC Cards-Adapter(21)

- Memory Connectors-PC Card Sockets(3299)

- Memory Connectors-Inline Modul Sockets(3390)

- LGH Steckverbinder(764)

- Keystone-Einsätze(2758)

- Keystone-Frontplatte, Frames(1926)

- Heavy Duty Steckverbinder-Einsätze, Module(4190)

- Schwerlastanschlüsse - Gehäuse, Kapuzen, Basen(17226)

- Heavy Duty Steckverbinder-Frames(523)

- Heavy Duty Steckverbinder-Kontakte(1832)

- Heavy Duty Steckverbinder-Baugruppen(671)

- LWL-Steckverbinder-Gehäuse(919)

- Glasfaser-Steckverbinder - Adapter(4455)

- LWL-Steckverbinder(3001)

- FFC, FPC (flache flexible) Steckverbinder - Gehäuse(652)

- FFC, FPC (flache flexible) Anschlüsse - Kontakte(202)

- FFC, FPC (flache flexible) Anschlüsse(18691)

- D-Sub, d-förmige Steckverbinder-Terminatoren(47)

- D-Sub, d-förmige Steckverbinder-Gehäuse(12238)

- D-Sub, d-förmige Steckverbinder-Kontakte(2714)

- D-Sub, D-förmige Steckverbinder-Rückenschalen, Kapuzen(5995)

- D-Sub, d-förmige Steckverbinder-Adapter(1304)

- D-Sub Steckverbinder(141346)

- D-förmige Steckverbinder-Centronics(8770)

- Kontakte, Frühling geladen und Druck(630)

- Kontakte-Multi Purpose(6196)

- Kontakte-"Leadframe"(122)

- Koaxial-Steckverbinder (RF)-Terminatoren(1231)

- Koaxial-Steckverbinder (RF)-Kontakte(480)

- Koaxial-Steckverbinder (RF)-Adapter(6386)

- Koaxialverbinder (RF)(25734)

- Rundsteckverbinder-Gehäuse(441226)

- Rundsteckverbinder-Kontakte(4737)

- Rundsteckverbinder-backschalen und Kabel-Klemmen(53692)

- Rundsteckverbinder-Adapter(8839)

- Rundanschlüsse(1196254)

- Card Edge Steckverbinder-Gehäuse(469)

- Karte Edge Verbinder-edgeboard Verbinder(672683)

- Card Edge Verbinder-Kontakte(325)

- Card Edge Verbinder-Adapter(73)

- Blade Type Power Steckverbinder-Gehäuse(837)

- Blade Type Power Connectors-Kontakte(393)

- Stromanbeter Blade Type(4163)

- Zwischen Serien-Adapter(649)

- Barrel-Stromanschluss(935)

- Barrel-Audio-Anschlüsse(2432)

- Barrel-Audio Adapter(92)

- Banana und Tip Steckverbinder-Buchsen, Stecker(1644)

- Banana and Tip Connectors-Binding Posts(239)

- Banana und Tip Steckverbinder-Adapter(75)

- Backplane Steckverbinder-spezialisiert(45586)

- Backplane Steckverbinder-Gehäuse(6863)

- Backplane Steckverbinder-Hard metrisch, Standard(6297)

- Backplane Steckverbinder-DIN 41612(9408)

- Backplane Steckverbinder-Kontakte(3583)

- Backplane Connectors-ARINC Einsätze(2357)

- Backplane Steckverbinder-ARINC(3789)

-

Widerstände

-

Kondensatoren

Kondensatoren

- Aluminium-Elektrolytkondensatoren(16817)

- Trimmer, Variable Kondensatoren(3151)

- Dünne Folien-Kondensatoren(3473)

- Tantal-Kondensatoren(136103)

- Tantal-Polymer-Kondensatoren(9778)

- Silizium-Kondensatoren(320)

- Niob Oxide Kondensatoren(330)

- Mica und PTFE Kondensatoren(9101)

- Folien-Kondensatoren(150406)

- Elektrische Doppelschichtkondensatoren (EDLC), Superkondensatoren(2782)

- Keramische Kondensatoren(833829)

- Kondensatoren-Netzwerke, Arrays(2383)

- Aluminium-Elektrolytkondensatoren(125325)

- Aluminium-Polymer-Kondensatoren(7544)

-

Transformatoren

-

Isolatoren

-

Kristalle, Oszillatoren, Resonatoren

-

Switches

Switches

- Verriegelungsschalter(2893)

- Emergency-Stop-Schalter (E-Stop)(1160)

- Kabelzugschalter(571)

- Toggle-Schalter(33608)

- Rändelrads Schalter(742)

- Schalter(14263)

- Snap-Aktion, Endschalter begrenzen(28077)

- Slide-Schalter(5166)

- Selector-Schalter(9720)

- Rotary Switches(13850)

- Rocker Schalter(53790)

- Drucktaste-Schalter-Hall-Effekt(127)

- Drucktaste Schalter(190826)

- Programmierbare Display-Switches(39)

- Navigations-Schalter, Joystick(1882)

- Magnetische, Reed-Schalter(1399)

- Keypad-Schalter(637)

- Keylock Schalter(3684)

- DIP Schalter(7747)

- Konfigurierbare Switch-Komponenten-Objektiv(1435)

- Konfigurierbare Schalter-Komponenten-Lichtquelle(1236)

- Konfigurierbare Switch-Komponenten-Contact Block(1401)

- Konfigurierbare Switch-Komponenten-Body(16077)

- Disconnect-Switch-Komponenten(2567)

-

Relais

Relais

- Sicherheitsrelais(1310)

- Reedrelais(1735)

- Hochfrequenz (RF) -Relais(1190)

- Schütze (Festkörper)(686)

- Schütze (elektromechanisch)(11952)

- Kfz-Relais(1881)

- Solid State Relais(10652)

- Signal-Relais, bis zu 2 Ampere(9149)

- Relay-Sockets(2075)

- Power Relays, über 2 Ampere(31604)

- E / A-Relaismodule(712)

- I/o-Relay-Module-Input(2)

- I/o-Relay-Modul-Racks(247)

Sprache auswählen

Aktuelle Sprache

Deutsch

- English

- Deutsch

- Italia

- Français

- 日本語

- 한국의

- русский

- Svenska

- Nederland

- español

- Português

- polski

- Suomi

- Gaeilge

- Slovenská

- Slovenija

- Čeština

- Melayu

- Magyarország

- Hrvatska

- Dansk

- românesc

- Indonesia

- Ελλάδα

- Български език

- Afrikaans

- IsiXhosa

- isiZulu

- lietuvių

- Maori

- Kongeriket

- Монголулс

- O'zbek

- Tiếng Việt

- हिंदी

- اردو

- Kurdî

- Català

- Bosna

- Euskera

- العربية

- فارسی

- Corsa

- Chicheŵa

- עִבְרִית

- Latviešu

- Hausa

- Беларусь

- አማርኛ

- Republika e Shqipërisë

- Eesti Vabariik

- íslenska

- မြန်မာ

- Македонски

- Lëtzebuergesch

- საქართველო

- Cambodia

- Pilipino

- Azərbaycan

- ພາສາລາວ

- বাংলা ভাষার

- پښتو

- malaɡasʲ

- Кыргыз тили

- Ayiti

- Қазақша

- Samoa

- සිංහල

- ภาษาไทย

- Україна

- Kiswahili

- Cрпски

- Galego

- नेपाली

- Sesotho

- Тоҷикӣ

- Türk dili

- ગુજરાતી

- ಕನ್ನಡkannaḍa

- मराठी

Wie gestalte ich einen 3-zu-8-Leitungsdecoder und einen Demultiplexer?

Zeit: 2025/05/23

Durchsuchen: 2,282

In der digitalen Elektronik ist die Fähigkeit, den Datenfluss selektiv zu steuern, nützlich, und hier kommen Decoder und Demultiplexer ins Spiel.Beide Komponenten bieten eine wichtige Rolle bei der Interpretation und Verteilung von binären Signalen, unabhängig davon, ob es sich um eine Ausgabe von vielen auswählt oder die Eingabedaten basierend auf Steuersignalen routet.In diesem Artikel wird die Arbeitsprinzipien, Designstrategien und Anwendungen von Decoder und Demultiplexern aufgebaut, angefangen von grundlegenden 1-zu-2-Schaltungen bis hin zu fortgeschritteneren 3-zu-8-Implementierungen, einschließlich praktischer Beispiele wie dem 74HC238

74HC238

XINBOLE

XINBOLE DIP16

In Stock: 13452 pcs

IC.

Katalog

Decoderübersicht

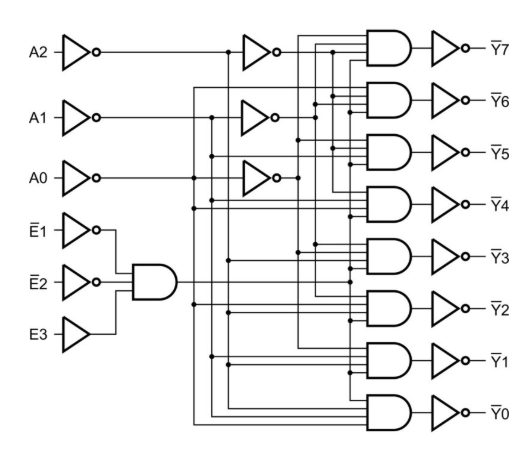

Ein Decoder ist eine digitale Schaltung, die Binäreingang nimmt und genau eine Ausgangsleitung aus vielen möglichen Optionen aktiviert.Wenn es gibt N Eingänge können die Schaltung erzeugen 2ⁿ Einzigartige Ausgänge, mit jeweils nur einer aktiv.Diese Art von Schaltung tut das Gegenteil von dem, was ein Encoder tut.

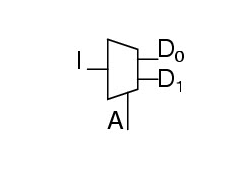

Abbildung 2. 1 bis 2 Decoderschaltung

Die meisten Decoder enthalten einen Bemessungsstift mit der Bezeichnung EN.Wenn EN niedrig ist (aus), sind alle Ausgänge gezwungen, bei 0 zu bleiben, unabhängig von den Eingangswerten.Dies stellt sicher, dass der Decoder nur dann reagiert, wenn sie ausdrücklich aktiviert sind.

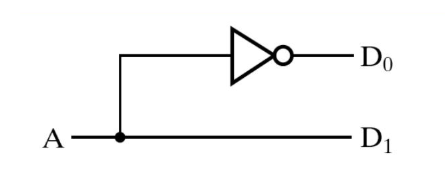

1-zu-2-Decoder

|

A |

D₁ |

D₀ |

|

0 |

0 |

1 |

|

1 |

1 |

0 |

In einem einfachen 1-zu-2-Decoder gibt es einen Eingang, der A und zwei Ausgänge, D₀ und D₁, genannt.Der Enable Pin (EN) steuert, ob der Decoder aktiv ist.

• Wenn a 0 und en hoch ist, setzt der Decoder D₀ auf 1 und d₁ auf 0.

• Wenn a 1 und en hoch ist, wird D₀ zu 0 und D₁ wird 1.

• Wenn EN niedrig ist, bleiben beide Ausgänge bei 0, unabhängig vom Wert von A.

Diese selektive Aktivierung stellt sicher, dass nur eine Ausgangsleitung den Eingang zu einem bestimmten Zeitpunkt widerspiegelt, sofern die Schaltung aktiviert ist.

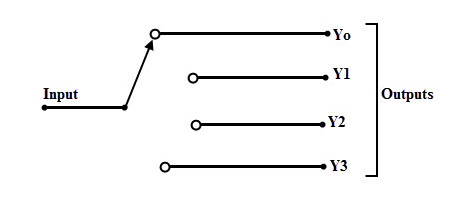

Demultiplexer verstehen

Abbildung 3. Demux

Ein Demultiplexer oder Demux nimmt ein einzelnes Eingangssignal an und leitet es zu einer von mehreren Ausgangsleitungen.Es verwendet Steuereingänge, um zu entscheiden, welche Ausgangsleitung das Signal empfangen soll.Während ein Multiplexer aus mehreren Eingängen und Treuungen in die Ausgabe ausgewählt wird, führt ein Demultiplexer umgekehrt. Er verbreitet einen einzelnen Eingang auf einen von vielen Ausgängen.

1-zu-2-Demultiplexer

Abbildung 4. 1 bis 2 Demux

In einem 1-zu-2-Demux gibt es einen Eingang, der i mit I und eine Kontrolllinie bezeichnet wird. Die Ausgabe geht an eine von zwei Zeilen, D₀ oder D₁.

|

ICH |

A |

D₀ |

D₁ |

|

0 |

0 |

0 |

0 |

|

0 |

1 |

0 |

0 |

|

1 |

0 |

1 |

0 |

|

1 |

1 |

0 |

1 |

• Wenn a 0 ist, wird die Eingabe I an D₀ übergeben.

• Wenn a 1 ist, werde ich an d₁ übergeben.

Der Demultiplexer trifft keine Entscheidungen - er folgt einfach dem Steuereingang, um das Signal zu vermitteln.

Entwerfen eines 3-zu-8-Line-Decoders

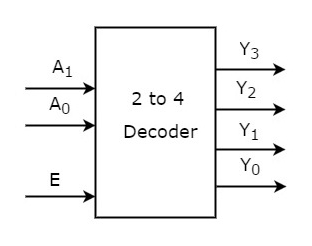

Um einen Decoder von 3 bis 8 Linien zu erstellen, ist es hilfreich, zunächst den einfacheren 2-zu-4-Decoder zu verstehen.Ein 2-zu-4-Decoder verfügt über zwei Eingänge mit der Bezeichnung A₁ und A₀ sowie ein Enable-Eingang. Die Schaltung erzeugt vier Ausgänge: Y₀, Y₁, Y₂ und Y₃.Wenn der Entzug der Aktivierung hoch ist, aktiviert der Decoder eine bestimmte Ausgangsleitung basierend auf der Kombination von A₁ und A₀.Alle anderen Ausgänge bleiben niedrig.

Abbildung 5. 2 Zeile zum 4 -Linie -Decoder

Logik hinter dem 2-zu-4-Decoder

Jeder Ausgang wird durch einen ausgeprägten logischen Ausdruck gesteuert, der aus den Eingängen und dem Aktivierungssignal erfolgt.Zum Beispiel:

• Y₃ schaltet sich nur ein, wenn E hoch ist, A₁ hoch und A₀ hoch ist.

• Y₂ wird eingeschaltet, wenn E hoch ist, A₁ hoch und a₀ niedrig ist.

• Y₁ wird eingeschaltet, wenn E hoch ist, a₁ niedrig und A₀ hoch ist.

• Y₀ schaltet sich ein, wenn alle drei Bedingungen erfüllt sind: E ist hoch, a₁ niedrig und a₀ niedrig.

|

E |

A₁ |

A₀ |

Y₃ |

Y₂ |

Y₁ |

Y₀ |

|

0 |

X |

X |

0 |

0 |

0 |

0 |

|

1 |

0 |

0 |

0 |

0 |

0 |

1 |

|

1 |

0 |

1 |

0 |

0 |

1 |

0 |

|

1 |

1 |

0 |

0 |

1 |

0 |

0 |

|

1 |

1 |

1 |

1 |

0 |

0 |

0 |

Diese Ausdrücke werden mit drei Eingängen und Toren implementiert.Die umgekehrten Formen der Eingänge A₁ 'und A₀' werden mit nicht Gates erstellt, so dass sowohl wahre als auch komplementierte Versionen jeder Eingabe verfügbar sind, wenn die richtige Logik für jeden Ausgang bildet.

Jeder Ausgang entspricht einer spezifischen Kombination der Eingänge, die als Minuteur bezeichnet werden.Da der Decoder nur einen Minuteur gleichzeitig aktiv ist, ist nur eine Ausgabe als Reaktion auf jedes Eingangspaar hoch, vorausgesetzt, die Schaltung ist aktiviert.Wenn E niedrig ist, reagiert keiner der Ausgänge;Sie alle bleiben bei Null.

Sie können diesen Ansatz erweitern, um einen 3-zu-8-Decoder zu entwerfen.Das Konzept ist das gleiche, aber jetzt mit drei Eingängen gibt es acht mögliche Eingabekombinationen.Die Schaltung hat acht Ausgänge, die jeweils an eine eindeutige Kombination dieser drei Eingangswerte gebunden sind.Genau wie im 2-zu-4-Decoder wird jeweils nur eine Ausgangsleitung aktiv, basierend auf den Binärwerten der Eingänge, vorausgesetzt, das Enable-Signal ist hoch.

Abbildung 6. Logikdiagramm von 2 bis 4 Decoder

Jeder Ausgang verwendet erneut ein Logik -Gate, das das Aktivierungssignal mit den drei Eingängen in ihren entsprechenden wahren oder komplementierten Formularen kombiniert.Dies garantiert eine genaue Kontrolle, wobei jede Eingangskombination genau einen Ausgang aktiviert und den Rest niedrig hält.

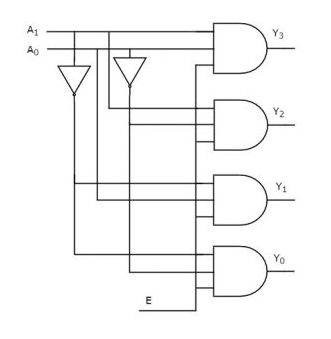

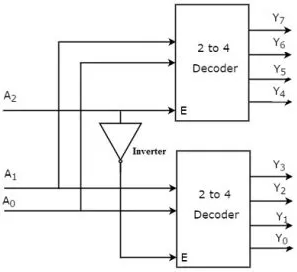

Implementierung eines 3-zu-8-Leitungsdecoders mit zwei 2-zu-4-Decodern

Um einen 3-zu-8-Leitungsdecoder zu erstellen, können Sie zwei 2-zu-4-Leitungsdecoder kombinieren.Dieser Ansatz verwendet drei Eingangssignale A₂, A₁ und A₀, um acht verschiedene Ausgänge zu erzeugen: y₀ bis y₇.Jeder Ausgang stellt eine der acht möglichen Kombinationen der drei Eingangsbits dar.

Um festzustellen, wie viele 2 bis 4 Decoder benötigt werden, berechnen Sie diese einfache Berechnung:

• Ein 2-zu-4-Decoder liefert 4 Ausgänge.

• Ein 3-zu-8-Decoder benötigt 8 Ausgänge.

Teilen Sie die Gesamtzahl der erforderlichen Ausgänge (8) durch die Anzahl der Ausgänge, die jeweils kleinerer Decoder (4) liefert (4), dass zwei Decoder erforderlich sind.

In diesem Setup:

• A₁ und A₀ dienen als Auswahleingänge und sind mit beiden Decodern verbunden.

• A₂ wirkt als Steuersignal, das feststellt, welcher Decoder aktiv ist.

Die Decoder sind so konfiguriert, dass:

• Wenn A₂ 0 ist, ist der erste Decoder aktiviert.Es erzeugt Ausgaben Y₀ bis Y₃ basierend auf den Werten von A₁ und A₀.

• Wenn A₂ 1 ist, wird der zweite Decoder aktiv.Es erzeugt Ausgänge y₄ bis y₇ mit den gleichen A₁- und A₀ -Eingängen.

Nur ein Decoder ist gleichzeitig aktiv.Dies wird in der Regel unter Verwendung von Aktivitäten der Aktivierung von Leitungen verwaltet, die auf A₂ reagieren.Wenn A₂ niedrig ist, wird die Aktivierung des ersten Decoders ausgelöst.Wenn A₂ hoch ist, ist es der zweite Decoder, der aktiviert wird.

Abbildung 7. 3 bis 8 Decoder mit 2 bis 4 Zeile

Mit dieser Methode können Sie einen komplexeren Decoder aus einfacheren, wiederverwendbaren Logikblöcken erstellen.Anstatt einen vollständigen 3-zu-8-Decoder von Grund auf neu zu entwerfen, erzielen Sie die gleiche Funktion, indem Sie zwei kleinere Decoder kombinieren und mit einem Teil des Eingangs steuern.Dieser modulare Ansatz spart den Designanstrengungen und reflektiert, wie digitale Systeme häufig verkleinert werden: durch das Komponieren kleinerer, gut verstandener Einheiten, um größere Aufgaben mit Präzision und Klarheit zu erledigen.

Erstellen eines 3-zu-8-Leitungsdecoders mit grundlegenden Logik-Toren

Ein 3-zu-8-Decoder ist eine digitale Schaltung, die drei Binäreingänge, die typischerweise A, B und C mit gekennzeichnet sind, einnimmt und genau eine von acht Ausgangsleitungen (D₀ bis D₇) basierend auf der Eingangskombination aktiviert.Dieses Setup stellt sicher, dass nur ein Ausgang zu einem bestimmten Zeitpunkt aktiv ist (hoch), während die verbleibenden Ausgänge inaktiv bleiben (niedrig).

|

A |

B |

C |

D0 |

D1 |

D2 |

D3 |

D4 |

D5 |

D6 |

D7 |

|

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

|

0 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

|

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

|

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

|

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

|

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

Der Decoder weist jede Ausgabe einer bestimmten Kombination der drei Eingangssignale zu.Um zu bestimmen, welcher Ausgang eingeschaltet wird, verwendet die Schaltung eine Mischung aus echten und invertierten Versionen der Eingänge.So wird jede Ausgabe gebildet:

• D₀ ist aktiv, wenn a, b und c alle 0 sind

• D₁ ist aktiv, wenn a und b 0 sind und C 1 ist 1

• D₂ ist aktiv, wenn a 0 ist, b 1 und c 0 ist 0

• D₃ ist aktiv, wenn a 0 ist, B 1 und C 1 ist 1

• D₄ ist aktiv, wenn a 1, B und C ist 0

• D₅ ist aktiv, wenn a 1, B 0 ist und C 1 ist 1

• D₆ ist aktiv, wenn a und b 1 sind und C 0 ist

• D₇ ist aktiv, wenn alle Eingänge 1 sind

Jede dieser Ausgangsbedingungen entspricht einer Minute der Eingangsvariablen, einer eindeutigen Kombination von A-, B- und C -Werten.

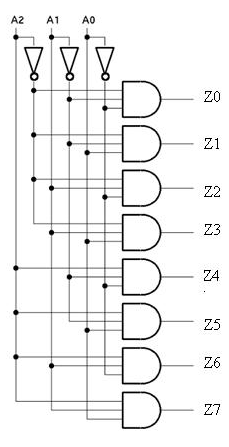

So erstellen Sie diesen Decoder mit einzelnen Logik -Toren:

• Erzeugen Sie umgekehrte Eingänge: Verwenden Sie drei keine Tore, um die umgekehrten Signale zu erzeugen: A ', B' und C '.Diese repräsentieren das logische Gegenteil jeder Eingabe und sind für die Abdeckung aller möglichen Eingangskombinationen erforderlich.

• Erstellen Sie die Ausgänge mit und Toren: Verwenden Sie acht und Tore, um die Ausgabestellen zu erstellen.Jedes Gate nimmt drei Eingänge ein-eine Mischung aus umgekehrten und nicht invertierten Signalen-, um eine bestimmte Festung zu erzeugen.Zum Beispiel:

• Das Tor, das D₀ erzeugt, nimmt ein ', B' und C '.

• Das Tor für D₇ nimmt A, B und C direkt.

Da jedes und Gate einer eindeutigen Eingangskombination entspricht, schließen sich die Ausgänge gegenseitig aus.Nur ein Gate gibt ein hohes Signal für einen bestimmten Eingang aus.

Diese Art von Schaltung wird oft als Decoder von Binär-Oktalen bezeichnet.Dies liegt daran, dass es eine 3-Bit-Binärzahl (von 000 bis 111) benötigt und sie in einen von acht Ausgängen umwandelt, die als Oktalstellen von 0 bis 7 dargestellt werden können. Dies macht es in Systemen nützlich, die Binärcodes in Signale für Anzeigen, Speicherauswahl oder Steuerlogie übersetzen müssen.

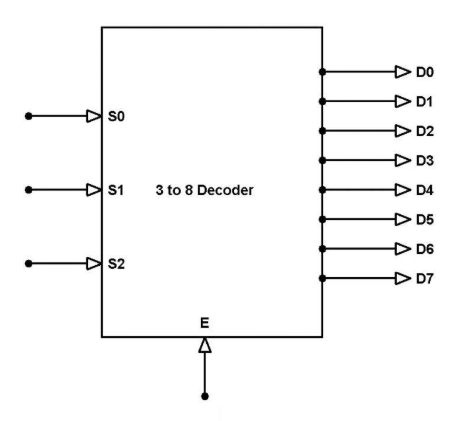

Blockdiagramm eines 3-zu-8-Leitungsdecoders blockieren

Ein 3-zu-8-Line-Decoder ist eine digitale Komponente, die drei Eingangssignale, die typischerweise S₂, S₁ und S₀ mit gekennzeichnet sind, aufnimmt und acht Ausgangssignale von d₀ bis d₇ erzeugt.Der Decoder enthält auch einen Aktivierungseingang, der häufig als E markiert ist. Dadurch ermöglicht der verwendete Pin: Der Decoder erzeugt nur die Ausgabe, wenn E hoch ist (aktiv).Wenn das Aktivierungssignal niedrig ist, ändert sich keiner der Ausgänge.Sie alle bleiben bei Null.

Abbildung 8. 3 bis 8 Linien -Decoder -Blockdiagramm

Wenn der Decoder aktiviert ist, überprüft er das von den drei Eingangsleitungen gebildete binäre Muster.Basierend auf dieser Kombination aktiviert es eine bestimmte Ausgangsleitung.Wenn der Eingang beispielsweise 101 ist, ist die Ausgabe d₅ hoch;Alle anderen werden niedrig bleiben.Dieses Verhalten ermöglicht es dem Decoder, eine einzelne Linie aus einer Gruppe von acht zu isolieren und zu steuern, die auf einem einfachen 3-Bit-Eingang basiert.

Diese One-Hot-Ausgangskonfiguration, bei der zu jeder Zeit nur eine Zeile hoch ist, ist für viele digitale Systeme nützlich, die ein Element aus einer Gruppe auswählen müssen, z. B. Speicherorte oder Steuerpfade.

Im Inneren des Decoders ist ein Netzwerk grundlegender Logik -Gates für die Generierung der Ausgänge verantwortlich.Nicht Gates werden verwendet, um die invertierten Versionen der Eingangssignale zu erstellen.Diese umgekehrten und nicht invertierten Signale werden dann in und Gates eingespeist, die so konfiguriert sind, dass jede spezifische Kombination der Eingänge erfasst.

Abbildung 9. 3 bis 8 Decoder -Schaltung

Einige Decoder-Designs verwenden NAND-Gates möglicherweise als Teil der logischen Optimierungen, je nachdem, ob die Ausgänge aktiv oder aktiv sind.Unabhängig von den verwendeten Gate -Typen entspricht jede Ausgangsleitung einer eindeutigen Kombination der drei Eingänge, um sicherzustellen, dass nur diese Linie aktiv wird.

3-zu-8-Zeilendecoder mit Wahrheitstabelle

Ein 3-zu-8-Line-Decoder ist ein digitales Logikgerät, das drei binäre Eingänge, S₂, S₁ und S₀, einnimmt und sie verwendet, um genau eine von acht möglichen Ausgängen zu aktivieren, die D₀ bis D₇ bezeichnet.Diese Art von Decoder ist nützlich, wenn ein System eine Option von vielen unter Verwendung einer kleinen Anzahl von Kontrolllinien auswählen muss.

Der Decoder enthält eine Aktivitätseingabe, die als E -markiert ist. Dieses Aktivierungssignal wirkt wie ein Gatekeeper:

• Wenn E niedrig ist (0), bleibt der Decoder inaktiv und alle Ausgänge bleiben bei niedrig, unabhängig von den Eingangswerten.

• Wenn E hoch ist (1), wird der Decoder aktiv und verwendet die drei Eingangsbits, um zu bestimmen, welcher der acht Ausgänge eingeschaltet werden soll (hoch eingestellt).Alle anderen Ausgänge bleiben aus (niedrig).

Jede einzigartige Kombination von S₂, S₁ und S₀ entspricht einem bestimmten Ausgang hoch.Das Design stellt sicher, dass nur eine Ausgabe gleichzeitig aktiv ist, was für ein eindeutige Signalrouting in digitalen Systemen wichtig ist.

Eingabe-Output-Zuordnung (Wahrheitstabelle)

Die folgende Tabelle zeigt, wie die Eingangssignale und der Aktivpin zusammenarbeiten, um die Ausgänge zu erzeugen:

|

S0 |

S1 |

S2 |

E |

D0 |

D1 |

D2 |

D3 |

D4 |

D5 |

D6 |

D7 |

|

X |

X |

X |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

|

0 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

|

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

|

1 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

|

1 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

|

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

HINWEIS: Ein "X" in der Spalte aktivieren bedeutet, dass die Eingangswerte keine Rolle spielt, ob E niedrig ist - nicht der Ausgänge werden aktiviert.

Diese Decoderstruktur ist besonders bei Mikroprozessoren und eingebetteten Systemen nützlich, bei denen die effiziente Steuerung mehrerer Linien mit minimalen Eingängen ein Muss ist.

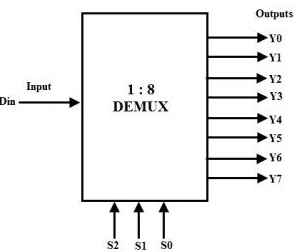

1-zu 8 Demultiplexer (Demux)

Ein 1-zu-8-Demultiplexer ist eine digitale Schaltung, die ein einzelnes Eingangssignal aufnimmt und es in eine von acht möglichen Ausgangsleitungen weiterleitet.Der Ausgang, der das Signal empfängt, hängt von der Kombination von drei Kontrollsignalen S₂, S₁ und S₀ ab, die als ausgewählte Linien bezeichnet werden.

Abbildung 10. 1 bis 8 Demux

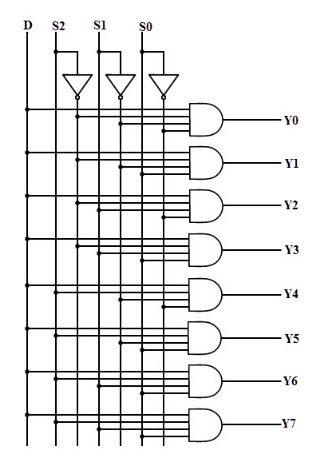

Der Demultiplexer verfügt über eine Dateneingabe, die häufig mit DIN bezeichnet wird, und acht Ausgänge, die Y₀ bis Y₇ bezeichnet haben.Die Rolle der ausgewählten Linien besteht darin, zu entscheiden, welcher Ausgang das Eingangssignal tragen soll.Zu einem bestimmten Zeitpunkt ist nur ein Ausgang aktiv, was bedeutet, dass es das Eingangssignal widerspiegelt.Alle anderen Ausgänge bleiben niedrig.

Innerhalb des Stromkreises arbeiten mehrere und Tore zusammen, um dieses Verhalten zu verwalten.Jedes und Tor entspricht einer der acht Ausgangsleitungen.Das Eingangssignal ist mit all diesen Toren verbunden, aber nur ein Tor darf das Signal an seinen Ausgang weiterleiten.Diese Steuerung wird erreicht, indem die Eingabe mit einer eindeutigen Kombination aus ausgewählten Linien kombiniert wird, von denen einige umgekehrt werden können.

Abbildung 11. 1 bis 8 Demux -Schaltung

Um diese Logik zu unterstützen, werden keine Gates verwendet, um die invertierten Versionen der Auswahlsignale bei Bedarf zu erstellen.Diese werden mit den ursprünglichen Auswahllinien kombiniert, so dass jedes und Gate nur einschalten, wenn die spezifische Kombination von Eingängen mit der ausgewählten Adresse übereinstimmt.Wenn die ausgewählten Linien beispielsweise einen Binärwert von 101 haben, aktiviert das Gate, das y₅ ausgibt, das Eingangssignal durch.Alle anderen Tore bleiben aus.

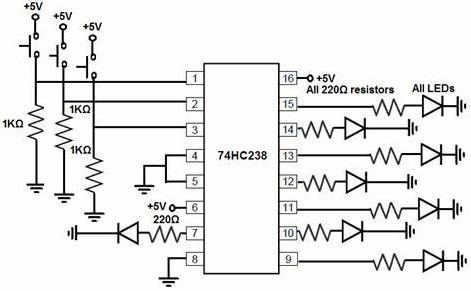

3-zu-8-Decoder/Demux-Schaltung mit 74HC238

Abbildung 12. 3 bis 8 Decoder/Demux-Schaltung mit 74HC238

74HC238

XINBOLE

XINBOLE DIP16

In Stock: 13452 pcs

Der 74HC238 ist ein vielseitiger Logikchip, der sowohl als 3-zu-8-Linie-Decoder als auch als 1-zu-8-Demultiplexer dienen kann.Dies macht es zu einem nützlichen Baustein in vielen digitalen Systemen, die eine kontrollierte Signalauswahl oder -verteilung erfordern.Dieser Chip verwendet drei binäre Eingänge mit der Bezeichnung A0, A1 und A2, um acht Ausgangsleitungen mit dem Namen Y₀ bis Y₇ zu steuern.Zu einem bestimmten Zeitpunkt wird nur ein Ausgang aktiv (hoch), basierend auf der Kombination der Eingangswerte.Der Rest der Ausgänge bleibt niedrig.Diese Art von Ausgangsmuster wird als "One-HOT" -Kodierung bezeichnet.

Der 74HC238 enthält auch drei Aktivierungseingänge.Diese Aktivalen wirken als zusätzliche Bedingungen, die für die Funktionsweise der Decoder- oder Demux -Funktion erfüllt werden müssen.Wenn die Aktivitäten nicht korrekt eingestellt sind, bleiben alle Ausgänge unabhängig von den Eingangswerten niedrig.Mit dieser Funktion kann der Chip in größeren Systemen verwendet werden, in denen mehrere Decoder zusammen verwaltet werden müssen (ein Prozess, der als Cascading bezeichnet wird).

Bei der Verwendung als Demultiplexer wirken die drei Eingangslinien als Auswahlsteuerungen.Eine einzelne Dateneingabe wird intern mit allen Ausgangsleitungen verbunden, aber nur die dem aktuellen Eingangskombination entsprechende Signal empfängt das Signal.Die verbleibenden Ausgänge bleiben inaktiv.Dies macht den IC nützlich, um einen Datenstrom auf ein bestimmtes Ziel zwischen mehreren Optionen zu lenken.

PIN -Layout und Konfiguration

Der 74HC238 wird in einem Standard-16-poligen Dual-In-Line-Paket (DIP) ausgestattet, das in Brotboards oder Durchleitungsschaltplatten leicht zu handhaben ist.Die Stifte werden wie folgt zugewiesen:

• Drei Adressleitungen (Eingabe): A0, A1, A2

• Drei Leitungen aktivieren: Oft verwendet, um mehrere Chips zu kontrollieren oder zu kaskade

• Acht Ausgänge: Y₀ durch y₇, alle aktiv hoch

Nach dem anderen ist nur ein Ausgang hoch und nur, wenn die Aktivierungseingänge ordnungsgemäß eingestellt sind.

Im Inneren des Chips vergleicht eine Kombination von Logik -Gates den aktuellen Eingangszustand mit jeder möglichen Ausgangsbedingung.Wenn die Eingangskombination mit dem zugewiesenen Muster eines bestimmten Ausgangs übereinstimmt und die Aktivierungseingänge aktiv sind, wird diese Ausgangsleitung hoch angetrieben.Alle anderen bleiben niedrig.Dies garantiert eine zuverlässige Aktivierung von One-at-a-Time-Ausgängen.

Vorteile und Anwendungsfälle

• Doppelfunktionalität: Kann als Decoder oder Demultiplexer fungieren

• Aktive Ausgänge: Vereinfacht die Verbindung zu anderen Logikschaltungen

• Unterstützt das Kaskadieren: Aktivieren Sie die Stifte ermöglichen eine Ausdehnung in größere Adressbereiche

• Zuverlässige Signalrouting: Sicherstellen Sie die saubere Ein-Linie-Aktivierung für Kontrollaufgaben

Dieser Chip ist besonders in digitalen Systemen nützlich, bei denen Signale genau gerichtet werden müssen, z.Das kompakte Design und die breite Kompatibilität machen es zu einer beliebten Wahl für Sie, von eingebetteten Systemen bis hin zu größeren digitalen Frameworks zu arbeiten.

Verwendung von Decoder und Demultiplexern

Decoder

• Analog-Digital-Konvertierung (ADC-Systeme): In ADC -Schaltungen helfen Decoder bei der Übersetzung analoge Signalpegel in bestimmte digitale Ausgänge.Jeder digitale Ausgang entspricht einem Bereich der analogen Eingangswerte, sodass das System den tatsächlichen Signalen wie Spannung oder Temperatur Binärcodes zuweisen kann.

• CPU -Steuereinheiten: Decoder sind in der Steuereinheit einer CPU nützlich.Sie nehmen Binäranweisungscodes wie die aus dem Speicher abgerufenen Anweisungscodes und konvertieren sie in individuelle Steuersignale, die bestimmte Hardwareaktionen auslösen, z. B. das Lesen von Daten aus dem Speicher oder die Ausführung arithmetischer Operationen.

• Digitale Logik- und Datenpfadregelung: In breiteren Logiksystemen werden Decoder verwendet, um bestimmte Subsysteme oder Datenpfade zu aktivieren oder auszuwählen.Beispielsweise können sie einen Speicherblock unter mehreren aktivieren oder bestimmen, welche Schaltung die Eingabe zu einem bestimmten Zeitpunkt empfängt.Diese selektive Aktivierung hilft, die Kontrolle innerhalb der digitalen Architekturen zu optimieren.

Demultiplexer

• Datenverteilung und Routing: Demultiplexer sind ideal, um eine einzelne Datenquelle an eine von vielen Zielen zu senden.Dies ist meistens nützlich, wenn nur ein Ausgabegerät gleichzeitig Daten empfangen sollte, z. B. in der Anzeigesteuerung oder in der peripheren Verwaltung.

• Kommunikationssysteme: In Kommunikationsnetzwerken helfen Demultiplexer bei der Zeitabteilung Multiplexing.Sie trennen einen kombinierten seriellen Stream in einzelne Datenkanäle.Dies erleichtert das Verwalten mehrerer Signale mit einem gemeinsam genutzten Übertragungsmedium.

• Seriell-parallele Konvertierung: Demultiplexer konvertieren auch serielle Daten in eine parallele Form, indem sie eingehende Bits über mehrere Ausgangsleitungen hinweg verteilen.Dies ist nützlich in Systemen, die eine parallele Verarbeitung oder gleichzeitige Datenzugriff erfordern, z. B. Datenbusse oder digitale Anzeigen.

• Arithmetische Logikeinheiten (Alus): In einem Alu kann ein Demultiplexer verwendet werden, um auszuwählen, welche Arithmetik- oder Logikoperation durchgeführt werden soll.Basierend auf Kontrollsignalen stellt es sicher, dass die korrekte Funktionseinheit ohne Aktivierung anderer, die Verbesserung der Effizienz und die Verhinderung von Signalkonflikten eingesetzt wird.

Abschluss

Decoder und Demultiplexer mögen auf der Oberfläche einfach erscheinen, aber ihre Präzision im Umgang von Binäreingängen macht sie in allem von der CPU -Steuerungslogik bis hin zu Speicherzugriffs- und Kommunikationssystemen erforderlich.Unabhängig davon, ob Sie einen grundlegenden digitalen Schaltkreis erstellen oder ein komplexes eingebettetes System entwerfen, verstehen Sie, wie diese Geräte wirksam sind und wie Sie sie effizient skalieren oder integrieren können, um eine reibungslose und zuverlässige Signalmanagement in jeder digitalen Architektur zu gewährleisten.

Häufig gestellte Fragen [FAQ]

1. Wie viele 3 bis 8 Decoder werden benötigt, wenn Sie einen 6-zu-64-Decoder entwerfen?

Um einen 6- bis 64-Decoder mit 3 bis 8 Decoder zu entwerfen, benötigen Sie insgesamt 9 Decoder.Ein 3-zu-8-Decoder behandelt die oberen 3 Eingangsbits und fungiert als Blockwähler, indem sie einen seiner 8 Ausgänge aktivieren, während jede Ausgangsleitung einen von 8 zusätzlichen 3-zu-8-Decodern ermöglicht, die die unteren 3 Bits dekodieren, was insgesamt 64 eindeutige Ausgänge ergibt.

2. Wie viele 3-Zeilen- bis 8-Zeilen-Decoder sind für einen 1/32 Decoder benötigt?

Um einen 1-von-32-Decoder mit nur 3 bis 8-Decoder zu erstellen, benötigen Sie insgesamt 5.Ein Decoder ist so konfiguriert, dass er die oberen 2 Bits verarbeitet, und ermöglicht es, einen von vier verbleibenden Decodern zu ermöglichen, von denen jedes die unteren 3 Bit als Eingang nimmt und 8 Ausgänge generiert, wodurch 32 Ausgänge abgeholt werden.

3. Wie viele Tore sind für einen 38 -Decoder benötigt?

Ein 3-zu-8-Decoder benötigt 8 und Tore mit jeweils 3 Eingängen.Jedes und Gate erzeugt eine Ausgangsleitung, indem die drei Eingangsbits oder deren Ergänzungen logisch kombiniert werden, um einem bestimmten binären Muster zu entsprechen.

4. Was kann nicht als Decoder verwendet werden?

Ein Multiplexer kann nicht als Decoder verwendet werden.Dies liegt daran, dass ein Multiplexer einen Eingang auswählt, der an den Ausgang geleitet wird, während ein Decoder einen Ausgang basierend auf einem Binäreingang aktiviert.Ihre Kernfunktionen sind entgegengesetzt.

5. Unter welchen Umständen kann ein Decoder in einen Demultiplexer umgewandelt werden?

Ein Decoder kann als Demultiplexer verwendet werden, wenn er über eine Aktivitätseingabe verfügt, die Daten tragen kann, während die Binäreingangsleitungen verwendet werden, um auszuwählen, welche Ausgabestelle diese Daten tragen sollen.In diesem Setup wirkt die Enable -Zeile wie die Dateneingabe des Demux -Datens und die Eingabestellen bestimmen, wohin diese Daten unter den Ausgängen gesendet werden.

Verwandter Artikel

-

May 23 2025NEC Teil 1: Abzweigschaltung Design, Sicherheit und Coderegeln

Zweigschaltungen sind die Substanz eines beliebigen elektrischen Verteilungssystems und liefern Stromversorgungsschalter an die Geräte, die wir tägl... -

May 23 2025Phasenunterschied und seine Formel verstehen

Haben Sie jemals zwei Wellen auf einem Bildschirm gesehen, die nicht perfekt übereinstimmen?Darum geht es bei Phasenunterschied.Es zeigt uns, wie ein...

Verwandte -Produkte

PIC16F18856-I/MV

IC MCU 8BIT 28KB FLASH 28UQFN

XC5VLX155T-1FFG1738C

IC FPGA 680 I/O 1738FCBGA

V48C24C150A

IGBT Modules

UPD64084GC

NEC QFP

PT8300-S

PT8300-S PTC

BCM7631YKFEBG

BCM7631YKFEBG BROADCO

LA7796T-TLM-E

LA7796T-TLM-E SANYO

LPC2144FBD64

LPC2144FBD64 PHIL

UPD789176GA-E01-YEU

UPD789176GA-E01-YEU NEC

TMCMB1A336MTRF

CAP TANT 33UF 20% 10V 1411

KXCF5272VF66

MOTOROLA BGA

BDCN-20-13+

RF DIR COUPLER 360MHZ-1GHZ 6SMD

AZ6118-01F.R7GR

Relevanzprodukte

74HC238

XINBOLE DIP16

vorrätig: 896