Alle Kategorien

-

Integrierte schaltkreise (ICS)

Integrierte schaltkreise (ICS)

- Schnittstelle - Sensor, kapazitive Berührung(642)

- Spezialisierte ICS(12302)

- PMIC-Spannungsregler-besonderer Zweck(5644)

- PMIC-Spannungsregler-lineare Regler(793)

- PMIC-Spannungsregler-linear + Switching(1829)

- PMIC-Spannungsregler-linear(70981)

- PMIC-Spannungsregler-DC DC Switching Regulators(39569)

- PMIC-Regler-DC-DC-Switching-Controller(13507)

- PMIC-Spannungs-Referenz(9453)

- PMIC-v/f und f/v-Wandler(145)

- PMIC-Thermal Management(592)

- PMIC-Supervisor(47946)

- PMIC-RMS bis DC-Wandler(170)

- PMIC-Netzteil-Controller, Monitore(2104)

- PMIC-Power over Ethernet (PoE) Controller(1008)

- PMIC-Power Management-spezialisierte(7722)

- PMIC-Netzschalter, Treiber laden(7706)

- PMIC-PFC (Power Factor Correction)(1222)

- PMIC oder Steuerungen, ideale Dioden(705)

- PMIC-Motor-Treiber, Regler(4712)

- PMIC-Beleuchtung, Ballast-Regler(560)

- PMIC-LED-Treiber(7282)

- PMIC-Laser-Treiber(573)

- PMIC-Hot-Swap-Controller(2816)

- PMIC-Gate-Treiber(7083)

- PMIC-voll, Half-Bridge-Treiber(1342)

- PMIC-Energy Messung(654)

- PMIC-Display-Treiber(1435)

- PMIC-derzeitige Regulierung/Management(1481)

- PMIC-Batterie-Management(5553)

- PMIC-Ladegeräte(3831)

- PMIC-AC DC Konverter, Offline Schalter(4905)

- Memory-Controller(358)

- Memory-Konfigurations-Proms für FPGAs(639)

- Speicher-Akkus(13)

- Erinnerung(65694)

- Logic-universelle Bus-Funktionen(706)

- Logic-Übersetzer, Level-Shifter(2854)

- Logik-Specialty Logic(1870)

- Logik-Signal-Schalter, Multiplexer, Decoder(9420)

- Logic-Shift-Register(2665)

- Logic-Parity Generatoren und Checkers(335)

- Logic-multivibratoren(831)

- Logik-Latches(3658)

- Logik - Tore und Wechselrichter - Multifunktion, konfigurierbar(1687)

- Logik-Tore und Wechselrichter(16453)

- Logic-Flip Flops(7780)

- Logik-FIFOs Speicher(4240)

- Logik-Zähler, Trennlinien(3456)

- Logik-Vergleichsoperator(592)

- Logik-Puffer, Treiber, Receiver, Transceiver(17835)

- Linear-Video-Verarbeitung(2909)

- Linear-Vergleichsoperator(5084)

- Linear-analoge Multiplikatoren, Trennwände(263)

- Linear-Verstärker-Video Amps und Module(1905)

- Linear-Verstärker-Spezial-Zweck(1856)

- Linear - Verstärker - Instrumentierung, OP -Verstärker, Pufferverstärker(34236)

- Linear-Verstärker-Audio(4567)

- Interface-Voice Record und Playback(556)

- Schnittstelle - UARTs (Universal Asynchronous Receivers -Sender)(1237)

- Schnittstelle-Telecom(4467)

- Interface-spezialisierte(4833)

- Interface-Signal Terminatoren(333)

- Interface-Signal-Puffer, Repeater, Splitter(1449)

- Interface-Serializer, Deserializer(1480)

- Schnittstellen-Sensor und Detektor-Interfaces(1524)

- Interface-Module(169)

- Interface-Modems-ICS und Module(407)

- Interface-e/a-Expander(1136)

- Interface-Filter-aktiv(1226)

- Interface-Encoder, Decoder, Konverter(714)

- Interface-Treiber, Receiver, Transceiver(20755)

- Interface-Direct Digital Synthesis (DDS)(117)

- Interface-Controller(3628)

- Interface-Codecs(1676)

- Schnittstelle - Analoge Switches, Multiplexer, Demultiplexer(12567)

- Schnittstelle-analoge Schalter-spezieller Zweck(2533)

- Embedded-System on Chip (SoC)(4496)

- Embedded-PLDs (programmierbare Logik-Vorrichtung)(971)

- Embedded-Mikroprozessoren(10083)

- Embedded-Mikrocontroller-anwendungsspezifische(2275)

- Embedded-Mikrocontroller(99285)

- Eingebettet - Mikrocontroller, Mikroprozessor, FPGA -Module(1527)

- Eingebettet - FPGAs (Feldprogrammiergate -Array) mit Mikrocontrollern(81)

- Embedded-FPGAs (Field Programmable Gate Array)(27747)

- Embedded-DSP (Digital Signal Processors)(4081)

- Eingebettet - CPLDs (komplexe programmierbare Logikgeräte)(5187)

- Datenerfassung-Touch Screen Controller(1210)

- Datenerfassung-Digital to Analog Converter (DAC)(14419)

- Datenerfassung-digitale Potentiometer(6250)

- Datenerfassung-analog zu Digital Converters (ADC)(17776)

- Datenerfassung-analoges Frontend (AFE)(787)

- Datenerfassung-MDE/DACs-spezieller Zweck(3043)

- Clock/Timing-Uhren in Echtzeit(2446)

- Uhr/Timing - programmierbare Timer und Oszillatoren(23469)

- Clock/Timing-IC-Akkus(4)

- Takt/Timing-Delay Lines(1049)

- Uhr/Timing - Uhrengeneratoren, PLLS, Frequenzsynthesizer(32775)

- Clock/Timing-Clock Puffer, Treiber(4568)

- Clock/Timing-anwendungsspezifische(8652)

- Audio Spezial-Zweck(1564)

-

Diskrete Halbleiter-Produkte

Diskrete Halbleiter-Produkte

- Aktuelle Regulierung - Dioden, Transistoren(1090)

- Transistoren-besonderer Zweck(226)

- Transistoren-programmierbare Unijunction(48)

- Transistoren-jfets(1558)

- Transistoren-IGBTs-Einzel(4799)

- Transistoren-IGBTs-Module(63420)

- Transistoren-IGBTs-Arrays(26)

- Transistoren-FETs, MOSFETs-Einzel(48330)

- Transistoren-FETs, MOSFETs-RF(4903)

- Transistoren-FETs, MOSFETs-Arrays(6641)

- Transistoren-Bipolar (BJT)-einzeln, Pre-biased(4539)

- Transistoren-Bipolar (BJT)-Einzel(25800)

- Transistoren-Bipolar (BJT)-RF(2087)

- Transistoren-bipolare (BJT)-Arrays, Pre-biased(2115)

- Transistoren-bipolare (BJT)-Arrays(2310)

- Thyristor-triacs(4044)

- Thyristoren-SCRs-Module(3967)

- Thyristoren-SCRs(5436)

- Thyristoren-diacs, sidacs(319)

- Power Driver Module(1627)

- Dioden-zenerdioden-Einzel(87483)

- Dioden-zenerdioden-Arrays(2619)

- Dioden - variable Kapazität (Varik, Varaktoren)(1200)

- Dioden-RF(2753)

- Dioden-Gleichrichter-Einzel(67528)

- Dioden-Gleichrichter-Arrays(20581)

- Dioden-Brücke-Gleichrichter(11700)

-

RF/if und RFID

RF/if und RFID

- SIM -Karten für Abonnenten -Identifikationsmodul (SIM)(77)

- RF -Zirkulatoren und Isolatoren(1742)

- RFID, RF-Zugang, Monitoring-ICS(1550)

- RFID Transponder, Tags(747)

- RFID Lesegeräte(464)

- RFID -Bewertungs- und Entwicklungskits, Boards(30)

- RFID Antennen(329)

- RFI und EMI - Abschirm- und Absorbungsmaterialien(6444)

- HF und EMI-Kontakte, Fingerstock und Dichtungen(7497)

- RF Transmitter(668)

- RF Transceiver Module(6900)

- RF-Transceiver ICS(4169)

- HF-Schalter(9276)

- RF Shields(16401)

- HF-Receiver(1998)

- HF -Empfänger, Sender und Transceiver -Einheiten(2763)

- RF Power Divider/Splitter(1223)

- RF Power Controller ICs(86)

- HF-Modulatoren(710)

- HF-Mixer(2800)

- RF misc ICS und Module(3276)

- HF-Front-End (LNA + PA)(419)

- RF -Bewertungs- und Entwicklungskits, Boards(747)

- HF-gerichtete Kupplung(2718)

- RF Diplexer(1464)

- RF-Detektoren(412)

- RF-Demodulatoren(249)

- HF-Antennen(12319)

- HF-Verstärker(19651)

- Balun(1496)

- Dämpfungsglieder(4852)

-

Optoelektronik

Optoelektronik

- Optomechanisch(480)

- Leuchten(125)

- Laserdioden, Lasermodule - Laserlieferung, Laserfasern(345)

- Hene Lasersysteme(31)

- Hene Laserköpfe(27)

- Hintergrundbeleuchtung anzeigen(93)

- Xenon-Beleuchtung(387)

- Touchscreen-Overlays(453)

- Panel Indicators, Pilot Lights(75729)

- Optik-Remote-Phosphor-Lichtquelle(269)

- Optik-Reflektoren(665)

- Optik-leichte Rohre(5384)

- Optik-Objektive(4951)

- LEDs-Spacer, Unentschieden(2718)

- LEDs-Lamp-Ersetzungen(29718)

- LEDs - Leiterplattenindikatoren, Arrays, Lichtstäbe, Balkendiagramme(9083)

- LED-thermische Produkte(667)

- LED-Beleuchtung(64)

- LED-Beleuchtung-weiß(37580)

- LED-Beleuchtung-Farbe(4728)

- LED-Beleuchtung-Maiskolben, Motoren, Module(28735)

- LED-Anzeige-diskret(27601)

- Laserdioden, Module(1553)

- Lampen-Glühlampen, Neons(311004)

- Lampen-Kälte-Fluoreszenz (KKL) & UV(164)

- Wechselrichter(7728)

- Infrarot, UV, sichtbare Strahler(3871)

- Fiber Optics-Transmitter-Antrieb integriert(4085)

- Fiber Optics-Transmitter-diskrete(350)

- Fiber Optics-Transceiver Module(18758)

- Fiberoptik-Switches, Multiplexer, Demultiplexer(1387)

- Fiberoptik-Receiver(695)

- Fiberoptik-Dämpfung(654)

- Elektrolumineszenz(102)

- Display, Monitor-Interface Controller(98)

- Display-Module-Vakuum-Leuchtstofflampen (VFD)(249)

- Module anzeigen-LED Dot Matrix und Cluster(865)

- Display-Module-LED-Zeichen und numerische(5421)

- Display-Module-LCD, OLED, Graphic(4654)

- Display-Module-LCD, OLED-Zeichen und numerische(2202)

- Display-Blenden, Objektive(88)

- Adresse, Spezialität(458)

-

Sensoren, Wandler

Sensoren, Wandler

- Ultraschallempfänger, Sender - Industrial(115)

- Temperatursensoren - Thermostate - Mechanisch - Industrielles(3103)

- Temperatursensoren - Analog und digitaler Ausgang - Industrial(209)

- Näherungssensoren - Industrial(13611)

- Drucksensoren, Wandler - Industrie(26503)

- Optische Sensoren - Photonik - Zähler, Detektoren, SPCM (Einzelphotonzählmodul)(751)

- Optische Sensoren - Kameramodule(875)

- Magnetsensoren - Position, Nähe, Geschwindigkeit (Module) - Industrie(554)

- Kraftsensoren - Industrial(346)

- Flusssensoren - Industrielles(151)

- Float, Level Sensoren - Industrial(310)

- Encoder - Industrial(4980)

- Farbsensoren - Industrial(50)

- Berührungssensoren(100)

- Ultraschall-Receiver, Transmitter(2421)

- Temperatursensoren-Thermostat-Solid State(1096)

- Temperatursensoren-Thermostate-mechanisch(3397)

- Temperatursensoren - Thermoelemente, Temperatursonden(1921)

- Temperatursensoren - RTD (Widerstandstemperaturdetektor)(1525)

- Temperatursensoren-PTC-Thermistoren(2273)

- Temperatursensoren-ntc-thermistoren(13259)

- Temperatursensoren-Analog und Digital Output(3928)

- DMS(1399)

- Spezialisierte Sensoren(1861)

- Solarzellen(503)

- Schock-Sensoren(84)

- Sensor-Interface-Junction-Blöcke(2519)

- Sensor-Kabel-Baugruppen(22011)

- Proximity/Belegung Sensoren-fertige Einheiten(725)

- Näherungsschalter(2860)

- Drucksensoren, Wandler(11317)

- Positionssensoren - Winkel, lineare Positionsmessung(6022)

- Optische Sensoren-reflektierende-Logik-Ausgang(194)

- Optische Sensoren - reflektierend - analoge Ausgang(432)

- Optische Sensoren-Phototransistoren(1027)

- Optische Sensoren - Photointerrupter - Schlitztyp - Transistorausgang(1427)

- Optische Sensoren - Photointerrupter - Schlitztyp - Logikausgabe(1215)

- Optische Sensoren-Lichtschranke, Industrial(16763)

- Optische Sensoren-Photodioden(1543)

- Optische Sensoren-Foto-Detektoren-Remote Receiver(2605)

- Optische Sensoren-Foto-Detektoren-Logik-Ausgang(146)

- Optische Sensoren-Foto-Detektoren-CDs-Zellen(74)

- Optische Sensoren-Distanz-Messung(377)

- Optische Sensoren-Ambient Light, IR, UV Sensoren(1305)

- Multifunktions(558)

- Motion Sensors-Vibration(337)

- Motion Sensors-Tilt Schalter(67)

- Bewegungsmelder-optisch(719)

- Motion Sensors-Neigungssensoren(175)

- Motion Sensors-Imus (Trägheit-Maßeinheiten)(416)

- Motion Sensors-Kreisel(214)

- Motion Sensors-Beschleunigungsmesser(1911)

- Magnete-Sensor abgestimmt(119)

- Magnete-Multi Purpose(1965)

- Magnetische Sensoren-Schalter (Solid State)(3700)

- Magnetsensoren - Position, Nähe, Geschwindigkeit (Module)(5199)

- Magnetische Sensoren-linear, Kompass (ICS)(1247)

- Magnetsensoren - Kompass, Magnetfeld (Module)(35)

- LVDT -Wandler (linearer variabler Differentialtransformator)(204)

- IrDA Transceiver-Module(196)

- Bildsensor, Kamera(2235)

- Feuchtigkeit-Sensoren(1425)

- Gas-Sensoren(1217)

- Force Sensoren(188)

- Durchfluss-Sensoren(550)

- Float, Level Sensoren(1343)

- Encoder(6357)

- Staub-Sensoren(43)

- Aktuelle Wandler(3455)

- Color Sensoren(85)

- Verstärker(1905)

-

Anschlüsse, Verbindungen

Anschlüsse, Verbindungen

- USB, DVI, HDMI -Stecker(446)

- Festkörperbeleuchtungsstecker(555)

- Steckdosen für ICs, Transistoren(953)

- Steckbare Steckverbinder(1221)

- Photovoltaik (Solarpanel) Anschlüsse(136)

- Glasfaseranschlüsse(370)

- FFC, FPC (flache flexible) Anschlüsse(761)

- D-Sub, D-förmige Stecker(2887)

- Koaxialverbinder (RF)(2389)

- Rundanschlüsse(14162)

- Stromanbeter Blade Type(273)

- Stecker und Behälter(2597)

- USB, DVI, HDMI Stecker-Adapter(572)

- USB, DVI, HDMI -Stecker(4298)

- Klemmen-Wire to Board Steckverbinder(217)

- Klemmen-Draht-Steckverbinder(4322)

- Klemmen-Draht-Pin Stecker(328)

- Terminals-Revolver Steckverbinder(1273)

- Terminals-spezialisierte Steckverbinder(2042)

- Klemmen-Spaten Verbinder(3902)

- Klemmen-Löten/Stecker(345)

- Klemmen-Verschraubungen(745)

- Klemmen-Ring Steckverbinder(12596)

- Klemmen-rechteckige Steckverbinder(4747)

- Terminals - Schnellverbindungen, schnelle Trennungsanschlüsse(8514)

- Klemmen-PC PIN, Single Post Connectors(3776)

- Klemmen-PC-Pin-Buchsen, Sockel-Steckverbinder(5883)

- Klemmen-magnetische Draht-Steckverbinder(1653)

- Klemmen-Messer Steckverbinder(112)

- Klemmen-Gehäuse, Stiefel(2850)

- Klemmen-Folie Steckverbinder(108)

- Klemmen-Barrel, Bullet-Steckverbinder(1107)

- Klemmen-Adapter(137)

- Terminal-Streifen und Revolver-Boards(1159)

- Terminal Junction Systeme(2533)

- Anschlussblöcke-Draht an Bord(43615)

- Terminal Blocks-spezialisierte(3722)

- Terminal Blocks-Power Distribution(847)

- Anschlussblöcke-Panel Mount(1359)

- Terminal Blocks-Interface Module(1819)

- Anschlussblöcke-Kopfzeilen, Stecker und Buchsen(119920)

- Anschlussblöcke-DIN-Schiene, Kanal(9373)

- Anschlussblöcke-Kontakte(65)

- Anschlussblöcke-Barrier Blocks(47517)

- Anschlussblöcke-Adapter(1059)

- Solid State Lighting Verbinder-Kontakte(271)

- Festkörperbeleuchtungsstecker(1344)

- Buchsen für ICS, Transistoren-Adapter(275)

- Steckdosen für ICs, Transistoren(22148)

- Shunts, Jumper(907)

- Rechteckige Verbinder-Feder geladen(7721)

- Rechteckige Steckverbinder-Gehäuse(43023)

- Rechteckige Verbinder-Kopfzeilen, Spezial-PIN(6129)

- Rechteckige Anschlüsse - Header, Gefäße, weibliche Sockel(229601)

- Rechteckige Verbinder-Kopfzeilen, männliche Pins(543338)

- Rechteckige Anschlüsse - kostenloses Hängen, Panelhalterung(30142)

- Rechteckige Verbinder-Kontakte(10681)

- Rechteckige Anschlüsse - Board in, Direktdraht zum Board(2432)

- Rechteckige Verbinder-Adapter(475)

- Rechteckig - Brett zu Board -Steckern - Header, Behälter, weibliche Sockel(9)

- Rechteckig - Brett zu Board -Steckern - Header, männliche Stifte(2)

- Rechteckige Anschlüsse - Board -Abstandshalter, Stacker (Board zu Board)(238901)

- Rechteckige Anschlüsse - Arrays, Kantentyp, Mezzanin (Board zu Board)(37853)

- Stromanschluss-Eingänge, Steckdosen, Module(10310)

- Steckbare Steckverbinder(6049)

- Photovoltaik- (Solarpanel) Anschlüsse - Kontakte(77)

- Photovoltaik (Solarpanel) Anschlüsse(504)

- Modulare Steckverbinder-Verdrahtung Blöcke(99)

- Modulare Steckverbinder-Stecker(1674)

- Modulare Steckverbinder-Stecker Gehäuse(181)

- Modulare Steckverbinder-Buchsen mit magnetischen(10152)

- Modulare Steckverbinder-Buchsen(23416)

- Modulare Steckverbinder-Adapter(855)

- Memory Connectors-PC Cards-Adapter(21)

- Memory Connectors-PC Card Sockets(3299)

- Memory Connectors-Inline Modul Sockets(3390)

- LGH Steckverbinder(764)

- Keystone-Einsätze(2758)

- Keystone-Frontplatte, Frames(1926)

- Heavy Duty Steckverbinder-Einsätze, Module(4190)

- Schwerlastanschlüsse - Gehäuse, Kapuzen, Basen(17226)

- Heavy Duty Steckverbinder-Frames(523)

- Heavy Duty Steckverbinder-Kontakte(1832)

- Heavy Duty Steckverbinder-Baugruppen(671)

- LWL-Steckverbinder-Gehäuse(919)

- Glasfaser-Steckverbinder - Adapter(4455)

- LWL-Steckverbinder(3001)

- FFC, FPC (flache flexible) Steckverbinder - Gehäuse(652)

- FFC, FPC (flache flexible) Anschlüsse - Kontakte(202)

- FFC, FPC (flache flexible) Anschlüsse(18691)

- D-Sub, d-förmige Steckverbinder-Terminatoren(47)

- D-Sub, d-förmige Steckverbinder-Gehäuse(12238)

- D-Sub, d-förmige Steckverbinder-Kontakte(2714)

- D-Sub, D-förmige Steckverbinder-Rückenschalen, Kapuzen(5995)

- D-Sub, d-förmige Steckverbinder-Adapter(1304)

- D-Sub Steckverbinder(141346)

- D-förmige Steckverbinder-Centronics(8770)

- Kontakte, Frühling geladen und Druck(630)

- Kontakte-Multi Purpose(6196)

- Kontakte-"Leadframe"(122)

- Koaxial-Steckverbinder (RF)-Terminatoren(1231)

- Koaxial-Steckverbinder (RF)-Kontakte(480)

- Koaxial-Steckverbinder (RF)-Adapter(6386)

- Koaxialverbinder (RF)(25734)

- Rundsteckverbinder-Gehäuse(441226)

- Rundsteckverbinder-Kontakte(4737)

- Rundsteckverbinder-backschalen und Kabel-Klemmen(53692)

- Rundsteckverbinder-Adapter(8839)

- Rundanschlüsse(1196254)

- Card Edge Steckverbinder-Gehäuse(469)

- Karte Edge Verbinder-edgeboard Verbinder(672683)

- Card Edge Verbinder-Kontakte(325)

- Card Edge Verbinder-Adapter(73)

- Blade Type Power Steckverbinder-Gehäuse(837)

- Blade Type Power Connectors-Kontakte(393)

- Stromanbeter Blade Type(4163)

- Zwischen Serien-Adapter(649)

- Barrel-Stromanschluss(935)

- Barrel-Audio-Anschlüsse(2432)

- Barrel-Audio Adapter(92)

- Banana und Tip Steckverbinder-Buchsen, Stecker(1644)

- Banana and Tip Connectors-Binding Posts(239)

- Banana und Tip Steckverbinder-Adapter(75)

- Backplane Steckverbinder-spezialisiert(45586)

- Backplane Steckverbinder-Gehäuse(6863)

- Backplane Steckverbinder-Hard metrisch, Standard(6297)

- Backplane Steckverbinder-DIN 41612(9408)

- Backplane Steckverbinder-Kontakte(3583)

- Backplane Connectors-ARINC Einsätze(2357)

- Backplane Steckverbinder-ARINC(3789)

-

Widerstände

-

Kondensatoren

Kondensatoren

- Aluminium-Elektrolytkondensatoren(16817)

- Trimmer, Variable Kondensatoren(3151)

- Dünne Folien-Kondensatoren(3473)

- Tantal-Kondensatoren(136103)

- Tantal-Polymer-Kondensatoren(9778)

- Silizium-Kondensatoren(320)

- Niob Oxide Kondensatoren(330)

- Mica und PTFE Kondensatoren(9101)

- Folien-Kondensatoren(150406)

- Elektrische Doppelschichtkondensatoren (EDLC), Superkondensatoren(2782)

- Keramische Kondensatoren(833829)

- Kondensatoren-Netzwerke, Arrays(2383)

- Aluminium-Elektrolytkondensatoren(125325)

- Aluminium-Polymer-Kondensatoren(7544)

-

Transformatoren

-

Isolatoren

-

Kristalle, Oszillatoren, Resonatoren

-

Switches

Switches

- Verriegelungsschalter(2893)

- Emergency-Stop-Schalter (E-Stop)(1160)

- Kabelzugschalter(571)

- Toggle-Schalter(33608)

- Rändelrads Schalter(742)

- Schalter(14263)

- Snap-Aktion, Endschalter begrenzen(28077)

- Slide-Schalter(5166)

- Selector-Schalter(9720)

- Rotary Switches(13850)

- Rocker Schalter(53790)

- Drucktaste-Schalter-Hall-Effekt(127)

- Drucktaste Schalter(190826)

- Programmierbare Display-Switches(39)

- Navigations-Schalter, Joystick(1882)

- Magnetische, Reed-Schalter(1399)

- Keypad-Schalter(637)

- Keylock Schalter(3684)

- DIP Schalter(7747)

- Konfigurierbare Switch-Komponenten-Objektiv(1435)

- Konfigurierbare Schalter-Komponenten-Lichtquelle(1236)

- Konfigurierbare Switch-Komponenten-Contact Block(1401)

- Konfigurierbare Switch-Komponenten-Body(16077)

- Disconnect-Switch-Komponenten(2567)

-

Relais

Relais

- Sicherheitsrelais(1310)

- Reedrelais(1735)

- Hochfrequenz (RF) -Relais(1190)

- Schütze (Festkörper)(686)

- Schütze (elektromechanisch)(11952)

- Kfz-Relais(1881)

- Solid State Relais(10652)

- Signal-Relais, bis zu 2 Ampere(9149)

- Relay-Sockets(2075)

- Power Relays, über 2 Ampere(31604)

- E / A-Relaismodule(712)

- I/o-Relay-Module-Input(2)

- I/o-Relay-Modul-Racks(247)

Sprache auswählen

Aktuelle Sprache

Deutsch

- English

- Deutsch

- Italia

- Français

- 日本語

- 한국의

- русский

- Svenska

- Nederland

- español

- Português

- polski

- Suomi

- Gaeilge

- Slovenská

- Slovenija

- Čeština

- Melayu

- Magyarország

- Hrvatska

- Dansk

- românesc

- Indonesia

- Ελλάδα

- Български език

- Afrikaans

- IsiXhosa

- isiZulu

- lietuvių

- Maori

- Kongeriket

- Монголулс

- O'zbek

- Tiếng Việt

- हिंदी

- اردو

- Kurdî

- Català

- Bosna

- Euskera

- العربية

- فارسی

- Corsa

- Chicheŵa

- עִבְרִית

- Latviešu

- Hausa

- Беларусь

- አማርኛ

- Republika e Shqipërisë

- Eesti Vabariik

- íslenska

- မြန်မာ

- Македонски

- Lëtzebuergesch

- საქართველო

- Cambodia

- Pilipino

- Azərbaycan

- ພາສາລາວ

- বাংলা ভাষার

- پښتو

- malaɡasʲ

- Кыргыз тили

- Ayiti

- Қазақша

- Samoa

- සිංහල

- ภาษาไทย

- Україна

- Kiswahili

- Cрпски

- Galego

- नेपाली

- Sesotho

- Тоҷикӣ

- Türk dili

- ગુજરાતી

- ಕನ್ನಡkannaḍa

- मराठी

Leitfaden zu JK Flip-Flop-Schaltungen

Zeit: 2025/04/14

Durchsuchen: 4,675

Katalog

JK Flip-Flop-Übersicht

Ein JK Flip-Flop ist ein grundlegender Baustein in der digitalen Elektronik, insbesondere in Systemen, die im Laufe der Zeit binäre Daten speichern und verwalten müssen.Sie finden es oft in Zählern, Schichtregistern und Kontrolleinheiten, in denen die Verfolgung früherer Signale ernst ist.Im Gegensatz zum SR Flip-Flop vermeidet die JK-Version das Problem eines undefinierten Zustands, wenn beide Eingaben aktiv sind, was es in Designs zuverlässig macht.

Im Kern enthält der JK Flip-Flop ein einziges Bit-entweder eine 0 oder ein 1.. Was sie auseinander setzt, ist, wie es sowohl die aktuellen Eingänge als auch das Taktsignal verwendet, um zu entscheiden, ob sie den gespeicherten Wert aufbewahren, ändern oder umdrehen.Es reagiert nicht nur sofort.Das Timing und den vorherigen Zustand faktor, was es für Systeme geeignet ist, die auf die Erinnerung früherer Ereignisse beruhen.

Es hilft digitale Schaltkreise, die Aktionen zu erinnern, den Betrieb synchron zu halten und Entscheidungsaufgaben reibungsloser zu erledigen.Die hohen (1) und niedrigen (0) Signale sagen der Schaltung, was zu tun ist, und das JK Flip-Flop interpretiert diese Signale auf vorhersehbare, strukturierte Weise.Diese Zuverlässigkeit spielt in vielen Arten von elektronischen Systemen eine Schlüsselrolle, von einfachen Steuerungsschaltungen bis hin zu fortgeschritteneren Computeraufgaben.

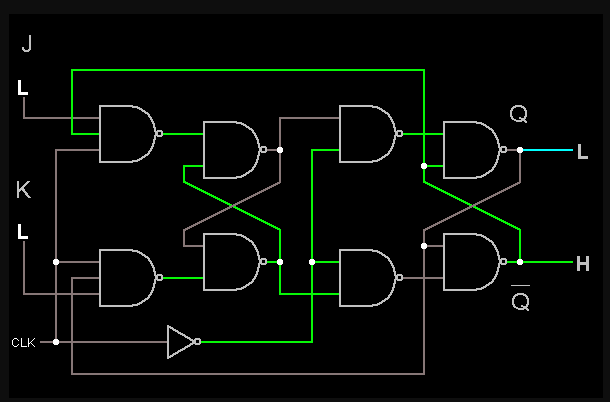

JK Flip-Flop-Symbol und logisches Verhalten

Das JK Flip-Flop wird von drei Haupteingängen gesteuert-J, K und einem Taktsignal-und erzeugt zwei Ausgänge: Q und seine inverse, oft mit q 'gekennzeichnete.Diese Eingänge und Ausgänge sind im Standard-Flip-Flop-Symbol deutlich gezeigt.Ein Schlüsselmerkmal in diesem Symbol ist der von Kanten ausgelöste Takteingang, der angibt, dass Änderungen der Ausgabe nur zu einem bestimmten Zeitpunkt auftreten-typisch an der steigenden Kante des Taktsignals.

Abbildung 2. JK Flip-Flop-Symbol

In Bezug auf die Funktion überwacht der JK Flip-Flop seine Eingänge nur, wenn die Uhr aktiv ist.Abhängig vom spezifischen Design kann dies bedeuten, wenn die Uhr hoch ist oder genauer gesagt, wenn sie von niedrig zu hoch wechselt.Wenn die Uhr inaktiv ist (normalerweise niedrig), hält der Flip-Flop ihren aktuellen Zustand.Mit anderen Worten, es erinnert sich an die letzte Ausgabe und ändert ihn erst, wenn der nächste aktive Taktpuls eintrifft.

Dieses kontrollierte Timing stellt sicher, dass Aktualisierungen der Ausgabe auf vorhersehbare und synchronisierte Weise auftreten.Die Ausgabe q verhält sich nur während der gültigen Taktphase nach den Werten von J und K.Die Beziehung zwischen Eingängen und Ausgabe ist in der folgenden Logiktabelle zusammengefasst:

|

J |

K |

Ausgabe q

Verhalten |

|

0 |

0 |

Keine Änderung (Riegel) |

|

0 |

1 |

Reset (q wird 0) |

|

1 |

0 |

Set (q wird 1) |

|

1 |

1 |

Schalter (Q Flips Status) |

Der letzte Fall - in dem sowohl J als auch K auf 1 gesetzt sind - ist besonders wichtig.Bei jedem Taktpuls wechselt der Ausgang Q auf seinen entgegengesetzten Wert.Mit dieser Umschaltaktion kann der JK Flip-Flop auf stabile, wiederholbare Weise zwischen 0 und 1 abwechseln.Es ist dieses Toggle-Verhalten, das den JK-Flip-Flop von der einfacheren SR-Flip-Flop unterscheidet, die keine sichere Antwort liefert, wenn beide Eingänge gleichzeitig aktiv sind.

Verständnis des JK Flip-Flop-Wahrheitstabelle

Die Wahrheitstabelle für ein JK Flip-Flop zeigt, wie sich der Ausgang basierend auf den Eingangswerten und dem aktuellen Zustand ändert.Es ordnet das Verhalten der Schaltung von der vorliegenden Ausgabe mit q (t) auf den nächsten Ausgang nach dem Taktimpuls mit q (t+1) ab.Dies hilft sich zu visualisieren, wie der Flip-Flop unter allen Eingangsbedingungen reagiert.

So wechselt der Flip-Flop von ihrem aktuellen Zustand in den nächsten Zustand:

|

J |

K |

Q (t) |

Q (t+1) |

|

0 |

0 |

0 |

0 |

|

0 |

0 |

1 |

1 |

|

0 |

1 |

X |

0 |

|

1 |

0 |

X |

1 |

|

1 |

1 |

0 |

1 |

|

1 |

1 |

1 |

0 |

In dieser Tabelle bedeutet der Buchstaben X, dass der aktuelle Zustand (q (t)) das Ergebnis nicht beeinflusst.In diesen Fällen hängt der nächste Zustand (q (t+1)) nur von den Eingangswerten ab und nicht von der vorherigen Ausgabe.

Wenn sowohl J als auch K auf 1 eingestellt sind, schaltet der Ausgang um.Dies bedeutet, dass Q auf das Gegenteil des Werts umschaltet, den er zuvor hatte.Wenn Q beispielsweise 0 war, wird es 1;Wenn es 1 war, wird es zu 0. Dies ist das Schlüsselverhalten, das den JK-Flip-Flop voneinander auszeichnet-es kann seine Ausgabe in jedem Taktzyklus zuverlässig abwechseln, wenn sie auf diese Weise konfiguriert werden.

Eigenschaften des JK Flip-Flops

Der JK Flip-Flop ist bekannt für eine Reihe von Funktionen, die es im Digital Circuit Design zuverlässig machen.Jedes dieser Eigenschaften ist nützlich, wie sich der Flip-Flop in praktischen Anwendungen verhält.

• Erstens funktioniert es als Speicherelement.Es enthält ein einziges Stück Daten - entweder eine 0 oder eine 1 -, bis ein neuer Befehl es sich ändern soll.Diese Fähigkeit, Status zu behalten, ist in sequentiellen Logiksystemen grundlegend, bei denen Schaltkreise an frühere Ereignisse oder Bedingungen erinnern müssen.

• Als nächstes reagiert der JK Flip-Flop nur in bestimmten Zeitpunkten in der Zeit, definiert durch die Taktsignal.Anstatt kontinuierlich zu reagieren, aktualisiert es seine Ausgabe nur, wenn die Taktkante auftritt, typischerweise auf dem steigenden oder fallenden Übergang.Dieses von Kanten ausgelöste Verhalten stellt sicher, dass der Schaltkreis auf kontrollierte und vorhersehbare Weise den Zustand ändert und unerwünschte oder zufällige Aktualisierungen verhindern.

• Ein weiteres wichtiges Merkmal ist die ITS Flexibilität.Abhängig von den Eingangswerten kann es einen festgelegten Betrieb ausführen (den Ausgang auf 1 erzwingen), einen Zurücksetzen (die Ausgabe auf 0 löschen) oder einen Umschaltungsvorgang (Schalten Sie den Ausgang in den gegenüberliegenden Zustand).Diese Kombination von Funktionen ermöglicht es dem JK Flip-Flop, sich an eine Vielzahl von Logikdesignanforderungen anzupassen.

• Im Gegensatz zu einigen anderen Flip-Flop-Typen tritt der JK Flip-Flop nie in eine ein undefinierter Zustand.Selbst wenn beide Eingänge aktiv sind, behandelt es die Situation mit einer klaren und erwarteten Reaktion, indem die Ausgabe umgeschaltet wird.Diese eingebaute Stabilität beseitigt das Risiko eines unvorhersehbaren Verhaltens, das die Leistung der Schaltung stören könnte.

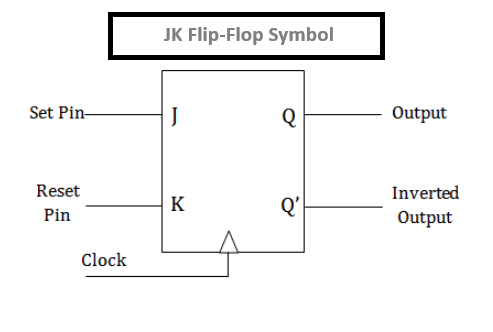

JK Flip-Flop Circuit Diagramm

Der interne Schaltkreis eines JK-Flip-Flops ist aus grundlegenden Logikstunden hergestellt, hauptsächlich NAND-Toren, kombiniert zu einem SR-Latch.Diese Struktur gibt dem Flip-Flop seine Speicher- und Steuerfunktionen.

Abbildung 3. JK Flip-Flop-Schaltplan

Damit die Schaltung nur bei bestimmten Timing -Ereignissen reagiert, werden die Eingänge j und k mit dem Taktsignal unter Verwendung von Logik -Toren kombiniert.Dieser Schritt stellt sicher, dass eine Änderung der Eingabe die Flip-Flop nur dann beeinflusst, wenn die Uhr aktiv ist.Mit anderen Worten, der Flip-Flop wartet auf einen Taktpuls, bevor er überlegt, seine Ausgabe zu aktualisieren.Diese Zeitsteuerung hilft dabei, den Betrieb über das System synchronisiert zu halten.

Sobald die Takteingänge verarbeitet sind, füttern sie in den SR -Latch.Der Latch hält die aktuelle Ausgabe und aktualisiert sie basierend auf den Logikbedingungen der Eingänge.Es bestimmt, ob der bestehende Zustand aufrechterhalten, die Ausgabe auf hoch eingestellt oder auf niedrig zurückgesetzt werden soll.

Ein wichtiger Teil dieser Schaltung ist die Rückkopplungsschleife.Die Ausgangssignale werden wieder in den Steuerpfad der Verriegelung weitergeleitet.Dieses Feedback ermöglicht die Umschaltfunktion.Wenn sowohl J als auch K aktiv sind (auf hoch eingestellt), veranlasst das Rückkopplungsmittel bei jedem Taktpuls in den gegenüberliegenden Zustand.Ohne diese Schleife wäre das Umschalten nicht möglich.

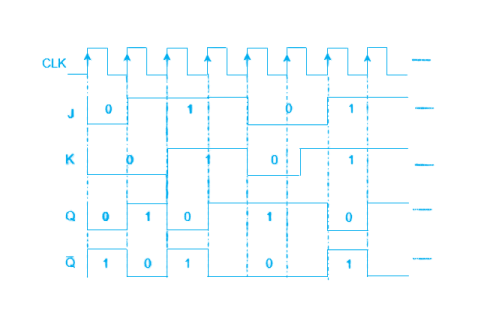

Interpretation des Timing-Diagramms eines JK Flip-Flops

Die Ausgabe eines JK Flip-Flop ändert sich gemäß der durch diesen Ausdruck definierten logischen Beziehung:

Qₙ₊₁ = j · q ' + k' · q

Diese Gleichung beschreibt, wie der nächste Ausgangswert q zum Zeitpunkt N+1 durch die aktuellen Eingangswerte J und K zusammen mit dem aktuellen Status von Q bestimmt wird. Sie mischt die SET- und Zurücksetzen in eine Regel und berücksichtigt auch die Umschaltfunktion.

Abbildung 4. Timing-Diagramm von JK Flip-Flop

Um besser zu verstehen, wie sich der Flip-Flop im Laufe der Zeit verhält, wird ein Zeitdiagramm verwendet.Dieses Diagramm zeigt eine Reihe von Wellenformen, die die Signale für J, K, Clock und die resultierende Ausgangs -Q darstellen. Durch das Lesen des Diagramms von links nach rechts können Sie sehen, wie der Schaltkreis als Eingangsbedingungen und die Taktsignalveränderung reagiert.

Der JK Flip-Flop aktualisiert nur die Ausgabe am steigenden Rand des Taktsignals.Das heißt, es beobachtet die Eingänge j und k kontinuierlich, reagiert jedoch nur dann, wenn die Uhr von niedrig zu hoch wechselt.In diesem Moment bewertet der Flip-Flop die Logikeingänge und entscheidet, ob der aktuelle Status beibehalten, die Ausgabe auf 1 einstellen, ihn auf 0 zurücksetzen oder umschalten oder umschalten.

Jede Änderung in der Ausgabe Q entspricht dem, was in der JK -Wahrheitstabelle gezeigt ist.Wenn J und K beide 0 sind, bleibt Q gleich.Wenn J 1 und K 0 ist, wird die Ausgabe eingestellt.Wenn J 0 und k ist 1, wird es zurückgesetzt.Und wenn beide Eingänge 1 sind, schaltet der Ausgang um.Diese Übergänge sind im Timing -Diagramm gekennzeichnet, sodass Sie visuell bestätigen können, wie Eingangswerte die Schaltung in jedem Taktzyklus beeinflussen.

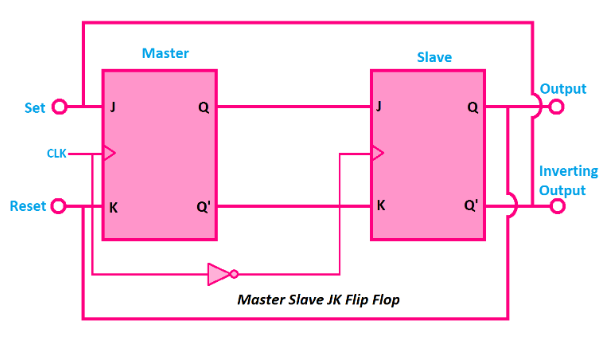

Master-Slave-Konfiguration in JK Flip-Flops

In Hochgeschwindigkeits-sequenziellen Schaltungen ist die Zeitgenauigkeit gefährlich.Ein häufiges Problem ist eine Rennbedingung-dies geschieht, wenn der Flip-Flop innerhalb eines einzelnen Taktzyklus zu schnell umschaltet und eine instabile oder unvorhersehbare Ausgabe verursacht.Um dies zu lösen, wird der Master-Slave JK Flip-Flop verwendet.Es bietet eine stabile, kontrollierte Methode, um Statusänderungen zu bewältigen, indem zwei Flip-Flops in einer Sequenz kombiniert werden.

Abbildung 5. Master-Slave JK Flip-Flop

Dieses Setup umfasst zwei Phasen: a Meister und ein Sklavebeide zusammenarbeiten, aber durch verschiedene Teile des Taktsignals ausgelöst.Der Master ist während der steigenden Kante der Uhr aktiv, was bedeutet, dass er Eingangswerte erfasst und hält, wenn der Takt von niedrig auf hoch wechselt.In der Zwischenzeit bleibt der Sklave in dieser Phase inaktiv.

Erst wenn die Uhr zu fallen beginnt - die sich von hoch zu niedrig schaltet - aktiviert der Sklave.Zu diesem Zeitpunkt nimmt es den vom Master gespeicherten Ausgang und wendet sie auf den Gesamtkreis an.Dieser zweistufige Prozess stellt sicher, dass sich der Ausgang in jedem Taktzyklus nur einmal ändert, sodass das Timing vorhersehbar bleibt und das Risiko eines schnellen Umschaltens beseitigt.

Hier ist eine vereinfachte Ansicht, wie sich der Master-Slave-JK-Flip-Flop unter verschiedenen Uhr- und Eingabebedingungen verhält:

|

Uhr |

J |

K |

Master

Aktion |

Sklave

Ausgabe |

|

0 |

X |

X |

Halten |

Halten |

|

1 |

0 |

1 |

Zurücksetzen |

Zurücksetzen |

|

1 |

1 |

0 |

Satz |

Satz |

|

1 |

1 |

1 |

Umschalten |

Umschalten |

In dieser Tabelle bedeutet "Halten" keine Änderung.Wenn die Uhr niedrig ist, bleibt das gesamte System im Leerlauf - keine Aktualisierungen.Sobald die Uhr hoch ist, bereitet der Meister den neuen Zustand basierend auf den Werten von J und K vor. Dann aktualisiert die Sklave die Ausgabe entsprechend.

Diese Architektur verbessert die Zuverlässigkeit von JK-Flip-Flops in schnellen Systemen erheblich.Durch die Aufteilung des Betriebs zwischen den steigenden und fallenden Kanten der Uhr fügt die Master-Slave-Konfiguration eine präzise Kontrolle über den Auftritt Statusänderungen hinzu, wodurch die Wahrscheinlichkeit von Timing-Fehlern verringert und saubere Übergänge gewährleistet werden.

Wie tritt Renne in JK Flip-Flops auf?

In digitalen Schaltkreisen, insbesondere solchen mit hoher Geschwindigkeit, ist eine genaue Kontrolle über das Timing ein Muss.Ein gemeinsames Problem, das diese Präzision stören kann, ist die Rennerkrankung.Dies geschieht, wenn der Taktpuls zu lange hoch bleibt, sodass der JK Flip-Flop ihre Ausgabe während eines einzelnen Zyklus mehr als einmal umschalten kann.Anstatt sauber zu wechseln, kann der Ausgang schnell hin und her umdrehen und ein instabiles und unvorhersehbares Ergebnis erzielen.

Dieses Verhalten tritt auf, da der Flip-Flop mit J und K auf 1 eingestellt ist und sich im Umschaltmodus befindet.Wenn die Uhr länger als die interne Antwortzeit aktiv bleibt, umschaltet der Schaltkreis, solange die Bedingungen unverändert bleiben.Diese wiederholte Umschaltung untergräbt die Zuverlässigkeit des Ausgangs, insbesondere in Systemen, die von exakten Zustandsübergängen abhängen.

Um Rassenbedingungen zu vermeiden, können mehrere Strategien angewendet werden:

• Master-Slave JK Flip-Flop: Diese Konfiguration unterteilt den Vorgang in zwei Phasen.Der Meister reagiert während der steigenden Kante der Uhr, während der Sklave das Ergebnis während der fallenden Kante überträgt.Dieses Setup garantiert nur eine Änderung pro Taktzyklus, wodurch die Wahrscheinlichkeit für mehrere Umschaltungen beseitigt wird.

• Kanten-ausgelöste Flip-Flops: Diese Entwürfe sind nur für den Moment des Übergangs empfindlich - entweder die steigende oder fallende Kante der Uhr -, nicht die Dauer des Taktpulses.Da sie ignorieren, wie lange die Uhr hoch oder niedrig bleibt, verhindern sie wiederholt während des Zyklus.

• Kürzere Uhrimpulse: Reduzierung der Länge des Taktsignals stellt sicher, dass der Umschaltungszustand nicht lange genug anhält, um mehrere Übergänge zu verursachen.Der Flip-Flop hat gerade genug Zeit, um einmal zu reagieren, bevor die Uhr in den inaktiven Zustand zurückkehrt.

Die Anwendung einer dieser Lösungen trägt dazu bei, einen stabilen und vorhersehbaren Betrieb aufrechtzuerhalten.In digitalen Umgebungen mit hohen Geschwindigkeiten sind sie besonders wichtig, in denen eine enge Timing-Steuerung für die korrekte Funktionsweise von Zählern, Registern und anderen sequentiellen Logikschaltungen erforderlich ist.

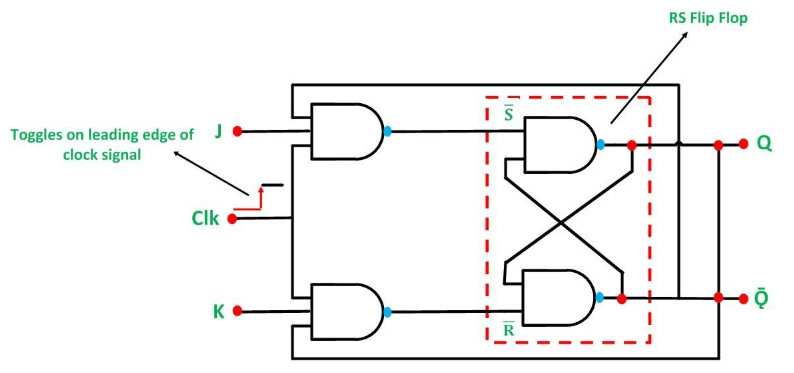

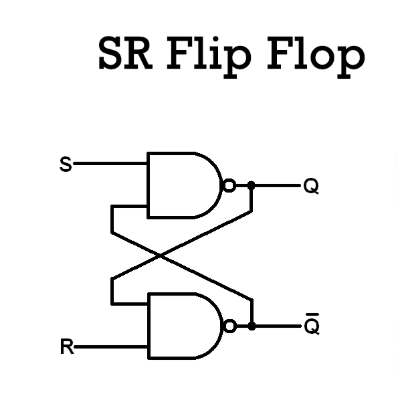

SR- und JK Flip-Flops-Unterschiede

Einer der wichtigsten Unterschiede zwischen dem SR- und JK-Flip-Flop liegt in der Art und Weise, wie die einzelnen Eingangskombinationen mit instabilen Ergebnissen führen können.

Abbildung 6. SR Flip-Flop

Im Fall der SR Flip-FlopEs gibt eine bekannte Einschränkung.Wenn sowohl die Eingänge der Sets als auch die Reset (R) gleichzeitig aktiv sind - sowohl auf Hochtouren ", tritt die Schaltung in einen undefinierten Zustand ein.Dies bedeutet, dass die Ausgänge Q und Q 'nicht mehr zuverlässig vorhergesagt werden können, was zu Instabilität in digitalen Systemen führen kann.Ein solches Verhalten ist in Designs, die von der präzisen Kontrolle und dem Zustand der Zustandsverfolgung abhängen, unerwünscht.

Hier ist eine vereinfachte Version des Ausgangsverhaltens des SR Flip-Flop:

|

S |

R |

Q (Ausgabe) |

Q'

(Ergänzen) |

|

0 |

0 |

0 |

1 |

|

0 |

1 |

0 |

1 |

|

1 |

0 |

1 |

0 |

|

1 |

1 |

Undefiniert |

Undefiniert |

Wie in der letzten Zeile gezeigt, wird die Ausgabe instabil, wenn beide Eingänge hoch sind - dies ist der Hauptnachteil der SR -Konfiguration.

Der JK Flip-Flop wurde speziell entwickelt, um dieses Problem zu lösen.Es baut auf den gleichen Grundprinzipien auf, führt jedoch eine intelligentere Antwort ein, wenn beide Eingänge hoch sind.Anstatt eine ungültige Ausgabe zu erzeugen, schaltet der JK Flip-Flop seine Ausgabe um.Das bedeutet, dass der Zustand von Q in das Gegenteil von dem, was es zuvor war.Dieses kontrollierte Verhalten ersetzt die Mehrdeutigkeit des SR-Flip-Flop durch ein zuverlässiges, genau definiertes Ergebnis.

Da es den undefinierten Zustand vollständig vermeidet, bietet der JK Flip-Flop eine sicherere und konsistentere Lösung für sequentielle Logikschaltungen.Es ist besonders nützlich in Hochgeschwindigkeitsanwendungen, bei denen Stabilität und vorhersehbare Ausgabe wichtig sind, um Systemfehler zu vermeiden und einen genauen Betrieb zu gewährleisten.

Vergleich von Flip-Flops und Riegel

Obwohl Flip-Flops und Verriegelung beide Binärdaten speichern, arbeiten sie auf unterschiedliche Weise und werden für unterschiedliche Zeitanforderungen in digitalen Systemen verwendet.

• A verriegeln ist ein asynchron Speicherelement.Dies bedeutet, dass seine Ausgabe aktualisiert werden, sobald sich die Eingabe ändert, ohne auf ein Taktsignal zu warten.Aus diesem Grund kann der Ausgang sofort auf Eingangsschwankungen reagieren, solange das Steuersignal dies zulässt.

• Andererseits a Flipflop ist a synchron Gerät.Es aktualisiert seine Ausgabe nur, wenn ein Taktsignal einen bestimmten Übergangspunkt erreicht - normalerweise eine steigende oder fallende Kante.Dieses Verhalten führt eine präzise Timing -Kontrolle ein und stellt sicher, dass Zustandsänderungen in vorhersehbaren Intervallen auftreten.

Die wichtigste Unterscheidung liegt darin, wie jeder auf Kontrollsignale reagiert.Riegel sind ebenenempfindlich;Sie reagieren je nach Design hoch oder niedrig, wenn der Steuereingang hoch oder niedrig gehalten wird.Im Gegensatz dazu sind Flip-Flops aus der Kante ausgelöst, was bedeutet, dass sie nur im Moment eines Taktsignalsübergangs reagieren.Diese Zeitbeschränkung macht Flip-Flops in synchronisierten digitalen Schaltkreisen zuverlässiger, insbesondere wenn saubere Übergänge und Widerstand gegen Eingangsrauschen ein Muss sind.

Es gibt auch verschiedene Arten von Resseln, die dadurch kategorisiert sind, wie sie auf das Steuersignal reagieren:

• Ein aktiver Verriegelung Ermöglicht die Durchführung von Daten, wenn das Steuersignal hoch ist.Wenn die Steuerung niedrig ist, hält oder sperrt sie den letzten Wert.

• Ein Active-T-Tiefe Latch arbeitet gegenüber.Es reagiert, wenn das Steuersignal niedrig ist und die Daten enthält, wenn das Signal auf Hoch zurückkehrt.

In Systemen, in denen präzise Timing und koordinierte Operationen nützlich sind-wie Zähler, Register und sequentielle Logikschaltungen-sind Flip-Flops im Allgemeinen die bevorzugte Wahl.Ihre von Kanten ausgelöste Natur bietet die Vorhersehbarkeit und Stabilität, die für ein genaues und wiederholbares Verhalten erforderlich ist, insbesondere bei Hochgeschwindigkeits- oder Rauschempfindlichkeiten.

Vorteile des JK Flip-Flop

Der JK Flip-Flop bietet mehrere Vorteile, die es besonders nützlich in sequentiellen digitalen Systemen machen, wobei Zuverlässigkeit und Timing schwerwiegend sind.

• Eine der wichtigsten Stärken ist, dass es tritt niemals in einen undefinierten Zustand ein.Im Gegensatz zum SR-Flip-Flop, der unvorhersehbar wird, wenn beide Eingänge aktiv sind, behandelt der JK Flip-Flop alle möglichen Eingangskombinationen mit klar definiertem Verhalten.Diese Vorhersehbarkeit sorgt für den stabilen Betrieb auch in komplexen Logikschaltungen.

• Ein weiteres wertvolles Merkmal ist seine Fähigkeit zu Schalten Sie die Ausgabe um.Wenn beide Eingänge auf hoch eingestellt sind, wechselt der Ausgang mit jedem Taktpuls in den entgegengesetzten Zustand.Dadurch ist der JK Flip-Flop ideal für die Verwendung in Binärzählern, Frequenzteilern und anderen Anwendungen, in denen abwechselnde Zustände benötigt werden.

• Der JK Flip-Flop ist auch Multifunktional.Es kann drei grundlegende logische Operationen ausführen - einsetzen, zurücksetzen und umschalten -, die von den Eingabebedingungen abhängig sind.Mit dieser Vielseitigkeit können Sie eine einzelne Komponente anstelle mehrerer Flip-Flop-Typen verwenden und das Schaltungsdesign vereinfachen.

• Schließlich ist es Kanal-ausgelöster Betrieb Fügt der Zeitsteuerung Präzision hinzu.Die Ausgabe aktualisiert nur einen bestimmten Übergang des Taktsignals, typischerweise die steigende Kante.Diese zeitliche Empfindlichkeit hilft bei der Reduzierung von Störungen und unerwünschten Veränderungen, die bei sensiblen Konstruktionen auf Niveau üblich sind.

Anwendungen von JK Flip-Flops

JK Flip-Flops werden aufgrund ihres zuverlässigen Betriebs und der Fähigkeit, mehrere Logikfunktionen auszuführen, häufig in der digitalen Elektronik verwendet.Ihr flexibles Verhalten macht sie in einer Vielzahl von sequentiellen Schaltungskonstruktionen wertvoll, bei denen Timing und Zustandskontrolle nützlich sind.

Zähler

Eine der häufigsten Verwendungszwecke von JK Flip-Flops ist die Zähler.In dieser Rolle reagieren sie auf Eingangsimpulse - oft von einem Taktsignal - und verfolgen die Anzahl der auftretenden Ereignisse oder Zyklen.Aufgrund ihrer Umschaltfunktionalität sind JK Flip-Flops besonders effektiv bei der Bauen von Binär- und Ripple-Zähler.

Schichtregister

Sie werden auch in Schichtregistern verwendet, bei denen sich Daten in einer kontrollierten Reihenfolge bewegen müssen - entweder ein Bit gleichzeitig oder über mehrere Bits parallel.JK Flip-Flops stellen sicher, dass sich jedes Bit im richtigen Moment verschiebt und die Datenintegrität über jeden Taktpuls aufrechterhalten wird.

Datenspeicherung und Übertragung

Eine weitere wichtige Anwendung ist in der Datenspeicherung und -übertragung.Ein einzelner JK-Flip-Flop kann ein Stück Daten zuverlässig speichern und seinen Wert hält, bis ein Taktsignal ein Update auffordert.Diese Funktion wird für die temporäre Datenspeicherung in Verarbeitungssystemen verwendet.

Frequenzteiler

JK Flip-Flops finden sich auch in Frequenzteilern, wo sie dazu beitragen, die Häufigkeit eines Hochgeschwindigkeits-Taktsignals zu verringern.Wenn Sie beispielsweise jeden zweiten oder vierten Taktimpuls umschalten, schneiden sie die Eingangsfrequenz effektiv um einen bestimmten Faktor aus.

Debouncing wechseln

Beim Switch -Debouncing werden sie verwendet, um laute Eingangssignale von mechanischen Schalter zu beseitigen.Diese Schalter erzeugen häufig schnelle, unvorhersehbare Spannungsänderungen, wenn sie gedrückt oder freigegeben werden.Ein JK Flip-Flop kann diese Schwankungen herausfiltern und eine saubere und stabile Ausgabe liefern.

Speicherelemente im Register

Schließlich dienen sie als Speicherelemente in Registern und halten vorübergehend Daten, die in einem digitalen System verarbeitet oder übertragen werden.Ihre Fähigkeit, Werte zu speichern und zu aktualisieren, ist vorhersehbar nützlich, um zuverlässige Steuereinheiten und Speicherkomponenten zu erstellen.

Abschluss

Der JK Flip-Flop zeichnet sich durch Vielseitigkeit, Stabilität und Fähigkeit aus, ohne Zweifel alle Eingabebedingungen zu behandeln.Die von Kanten ausgelöste Betrieb, Speicherfunktion und Umschaltungsfähigkeiten sind in Anwendungen erforderlich, die eine präzise Zeit- und Statusverwaltung erfordern.Von grundlegenden Binärzählern bis hin zu komplexen Kontrolleinheiten bietet dieser Flip-Flop eine zuverlässige Lösung zum Speichern und Übergang digitaler Daten.Da digitale Systeme in der Komplexität weiter wachsen, bleibt das Beherrschen von Komponenten wie dem JK Flip-Flop nützlich, um effiziente und zuverlässige Logikkreise zu entwerfen.

Häufig gestellte Fragen [FAQ]

1. Wann ist ein JK Flip-Flop in einem nicht änderischen Zustand?

Ein JK Flip-Flop befindet sich in einem Bedingungen ohne Änderung, wenn beide Eingänge J und K auf 0 eingestellt sind und ein Taktpuls angewendet wird.In diesem Zustand hält der Ausgang ihren vorherigen Wert ohne Umschalten und macht ihn nützlich, wenn der Flip-Flop vorübergehend seinen letzten Status ohne Update "erinnert".

2. Wie können wir das Problem von JK Flip-Flop entfernen?

Das Rennproblem des JK-Flip-Flop, das auftritt, wenn sowohl J als auch K 1 sind und der Taktpuls zu lang ist, kann durch Verwendung eines von Kanten ausgelösten JK-Flip-Flops oder einer Master-Sklaven-Konfiguration entfernt werden.Diese Versionen sorgen dafür, dass sich die Ausgabe während eines Taktzyklus nur einmal ändert und schnelle und unerwünschte Umschaltungen beseitigt.

3. Was wird in Flip-Flops ausgelöst?

Das Auslösen in Flip-Flops bezieht sich auf den genauen Moment, in dem der Flip-Flop den Eingang überprüft und die Ausgabe aktualisiert, die normalerweise vom Taktsignal gesteuert wird.Dies kann während des gesamten hohen oder niedrigen Pegels der Uhr (Levelauslöser) oder im Moment des Taktsignals von niedrig zu hoch oder hoch zu niedrig (Kantenauslöser) ändert, was eine genauere Zeitsteuerung in digitalen Schaltkreisen bietet.

4. Warum wird der JK Flip-Flop als Universal Flip-Flop bezeichnet?

Der JK Flip-Flop wird als Universal Flip-Flop bezeichnet, da er die Funktionen anderer Arten von Flip-Flops wie SR, D und T ausführen kann, indem sie einfach die Art und Weise ändern, wie die Eingänge verbunden sind.Diese Vielseitigkeit ermöglicht es in vielen verschiedenen Logik- und Speicheranwendungen, ohne separate Komponenten zu benötigen.

5. Ist die JK Flip-Flop-Kante ausgelöst?

Ja, der JK Flip-Flop ist typischerweise ausgestrahlt, was bedeutet, dass er auf einen bestimmten Übergang des Taktsignals reagiert, am häufigsten auf die steigende Kante.Dies stellt sicher, dass sich die Ausgabe nur in einem genauen Moment ändert und die Stabilität und Synchronisation in digitalen Systemen verbessert.

Verwandter Artikel

-

Apr 14 2025Wie entwerfe ich eine Leiterplatte mit einem stabilen 5 -V -Gleichstromeingang?

In der modernen Elektronik wird ein stabiler DC 5V -Eingang zum Einschalten von Mikrocontrollern, Sensoren und kompakten Systemen verwendet.Die weit v... -

Apr 13 2025Verwenden eines Multimeters für die Autodiagnose: eine Schritt-für-Schritt-Anleitung

In Fahrzeugen sind elektrische Systeme hilfreich - vom Start des Motors bis hin zur Leistung von Sicherheits- und Komfortmerkmalen.Wenn etwas schief g...

Verwandte -Produkte

TRJA226K006RRJ

CAP TANT 22UF 10% 6.3V 1206

STL100N8F7

MOSFET N-CH 80V 100A POWERFLAT

LTC1407ACMSE#PBF

IC ADC 14BIT PIPELINED 10MSOP

IDT79RC32V332-100DH

IC MPU INTERPRISE 100MHZ 208QFP

MAX3381ECUP+T

IC TRANSCEIVER FULL 2/2 20TSSOP

VE-JT0-EX

DC DC CONVERTER 5V 75W

UDN2987LW6T

UDN2987LW6T ALLEGRO

ICS476CG08L

ICS476CG08L ICS

BH7612FV-FE2

BH7612FV-FE2 ROHM

YL18-2050S

YULONG SOP16

T491C226K010ZT4678

CAP TANT 22.0UF 10.0V

FLL351ME

STE100PB2

ST QFP