Alle Kategorien

-

Integrierte schaltkreise (ICS)

Integrierte schaltkreise (ICS)

- Schnittstelle - Sensor, kapazitive Berührung(642)

- Spezialisierte ICS(12302)

- PMIC-Spannungsregler-besonderer Zweck(5644)

- PMIC-Spannungsregler-lineare Regler(793)

- PMIC-Spannungsregler-linear + Switching(1829)

- PMIC-Spannungsregler-linear(70981)

- PMIC-Spannungsregler-DC DC Switching Regulators(39569)

- PMIC-Regler-DC-DC-Switching-Controller(13507)

- PMIC-Spannungs-Referenz(9453)

- PMIC-v/f und f/v-Wandler(145)

- PMIC-Thermal Management(592)

- PMIC-Supervisor(47946)

- PMIC-RMS bis DC-Wandler(170)

- PMIC-Netzteil-Controller, Monitore(2104)

- PMIC-Power over Ethernet (PoE) Controller(1008)

- PMIC-Power Management-spezialisierte(7722)

- PMIC-Netzschalter, Treiber laden(7706)

- PMIC-PFC (Power Factor Correction)(1222)

- PMIC oder Steuerungen, ideale Dioden(705)

- PMIC-Motor-Treiber, Regler(4712)

- PMIC-Beleuchtung, Ballast-Regler(560)

- PMIC-LED-Treiber(7282)

- PMIC-Laser-Treiber(573)

- PMIC-Hot-Swap-Controller(2816)

- PMIC-Gate-Treiber(7083)

- PMIC-voll, Half-Bridge-Treiber(1342)

- PMIC-Energy Messung(654)

- PMIC-Display-Treiber(1435)

- PMIC-derzeitige Regulierung/Management(1481)

- PMIC-Batterie-Management(5553)

- PMIC-Ladegeräte(3831)

- PMIC-AC DC Konverter, Offline Schalter(4905)

- Memory-Controller(358)

- Memory-Konfigurations-Proms für FPGAs(639)

- Speicher-Akkus(13)

- Erinnerung(65694)

- Logic-universelle Bus-Funktionen(706)

- Logic-Übersetzer, Level-Shifter(2854)

- Logik-Specialty Logic(1870)

- Logik-Signal-Schalter, Multiplexer, Decoder(9420)

- Logic-Shift-Register(2665)

- Logic-Parity Generatoren und Checkers(335)

- Logic-multivibratoren(831)

- Logik-Latches(3658)

- Logik - Tore und Wechselrichter - Multifunktion, konfigurierbar(1687)

- Logik-Tore und Wechselrichter(16453)

- Logic-Flip Flops(7780)

- Logik-FIFOs Speicher(4240)

- Logik-Zähler, Trennlinien(3456)

- Logik-Vergleichsoperator(592)

- Logik-Puffer, Treiber, Receiver, Transceiver(17835)

- Linear-Video-Verarbeitung(2909)

- Linear-Vergleichsoperator(5084)

- Linear-analoge Multiplikatoren, Trennwände(263)

- Linear-Verstärker-Video Amps und Module(1905)

- Linear-Verstärker-Spezial-Zweck(1856)

- Linear - Verstärker - Instrumentierung, OP -Verstärker, Pufferverstärker(34236)

- Linear-Verstärker-Audio(4567)

- Interface-Voice Record und Playback(556)

- Schnittstelle - UARTs (Universal Asynchronous Receivers -Sender)(1236)

- Schnittstelle-Telecom(4467)

- Interface-spezialisierte(4833)

- Interface-Signal Terminatoren(333)

- Interface-Signal-Puffer, Repeater, Splitter(1449)

- Interface-Serializer, Deserializer(1480)

- Schnittstellen-Sensor und Detektor-Interfaces(1524)

- Interface-Module(169)

- Interface-Modems-ICS und Module(407)

- Interface-e/a-Expander(1136)

- Interface-Filter-aktiv(1226)

- Interface-Encoder, Decoder, Konverter(714)

- Interface-Treiber, Receiver, Transceiver(20755)

- Interface-Direct Digital Synthesis (DDS)(117)

- Interface-Controller(3628)

- Interface-Codecs(1676)

- Schnittstelle - Analoge Switches, Multiplexer, Demultiplexer(12567)

- Schnittstelle-analoge Schalter-spezieller Zweck(2533)

- Embedded-System on Chip (SoC)(4496)

- Embedded-PLDs (programmierbare Logik-Vorrichtung)(971)

- Embedded-Mikroprozessoren(10083)

- Embedded-Mikrocontroller-anwendungsspezifische(2275)

- Embedded-Mikrocontroller(99285)

- Eingebettet - Mikrocontroller, Mikroprozessor, FPGA -Module(1527)

- Eingebettet - FPGAs (Feldprogrammiergate -Array) mit Mikrocontrollern(81)

- Embedded-FPGAs (Field Programmable Gate Array)(27748)

- Embedded-DSP (Digital Signal Processors)(4081)

- Eingebettet - CPLDs (komplexe programmierbare Logikgeräte)(5187)

- Datenerfassung-Touch Screen Controller(1210)

- Datenerfassung-Digital to Analog Converter (DAC)(14419)

- Datenerfassung-digitale Potentiometer(6250)

- Datenerfassung-analog zu Digital Converters (ADC)(17776)

- Datenerfassung-analoges Frontend (AFE)(787)

- Datenerfassung-MDE/DACs-spezieller Zweck(3043)

- Clock/Timing-Uhren in Echtzeit(2446)

- Uhr/Timing - programmierbare Timer und Oszillatoren(23469)

- Clock/Timing-IC-Akkus(4)

- Takt/Timing-Delay Lines(1049)

- Uhr/Timing - Uhrengeneratoren, PLLS, Frequenzsynthesizer(32775)

- Clock/Timing-Clock Puffer, Treiber(4568)

- Clock/Timing-anwendungsspezifische(8652)

- Audio Spezial-Zweck(1564)

-

Diskrete Halbleiter-Produkte

Diskrete Halbleiter-Produkte

- Aktuelle Regulierung - Dioden, Transistoren(1090)

- Transistoren-besonderer Zweck(226)

- Transistoren-programmierbare Unijunction(48)

- Transistoren-jfets(1558)

- Transistoren-IGBTs-Einzel(4799)

- Transistoren-IGBTs-Module(63420)

- Transistoren-IGBTs-Arrays(26)

- Transistoren-FETs, MOSFETs-Einzel(48330)

- Transistoren-FETs, MOSFETs-RF(4903)

- Transistoren-FETs, MOSFETs-Arrays(6641)

- Transistoren-Bipolar (BJT)-einzeln, Pre-biased(4539)

- Transistoren-Bipolar (BJT)-Einzel(25800)

- Transistoren-Bipolar (BJT)-RF(2087)

- Transistoren-bipolare (BJT)-Arrays, Pre-biased(2115)

- Transistoren-bipolare (BJT)-Arrays(2310)

- Thyristor-triacs(4044)

- Thyristoren-SCRs-Module(3967)

- Thyristoren-SCRs(5436)

- Thyristoren-diacs, sidacs(319)

- Power Driver Module(1627)

- Dioden-zenerdioden-Einzel(87483)

- Dioden-zenerdioden-Arrays(2619)

- Dioden - variable Kapazität (Varik, Varaktoren)(1200)

- Dioden-RF(2753)

- Dioden-Gleichrichter-Einzel(67528)

- Dioden-Gleichrichter-Arrays(20581)

- Dioden-Brücke-Gleichrichter(11700)

-

RF/if und RFID

RF/if und RFID

- SIM -Karten für Abonnenten -Identifikationsmodul (SIM)(77)

- RF -Zirkulatoren und Isolatoren(1742)

- RFID, RF-Zugang, Monitoring-ICS(1550)

- RFID Transponder, Tags(747)

- RFID Lesegeräte(464)

- RFID -Bewertungs- und Entwicklungskits, Boards(30)

- RFID Antennen(329)

- RFI und EMI - Abschirm- und Absorbungsmaterialien(6444)

- HF und EMI-Kontakte, Fingerstock und Dichtungen(7497)

- RF Transmitter(668)

- RF Transceiver Module(6900)

- RF-Transceiver ICS(4169)

- HF-Schalter(9276)

- RF Shields(16401)

- HF-Receiver(1998)

- HF -Empfänger, Sender und Transceiver -Einheiten(2763)

- RF Power Divider/Splitter(1223)

- RF Power Controller ICs(86)

- HF-Modulatoren(710)

- HF-Mixer(2800)

- RF misc ICS und Module(3276)

- HF-Front-End (LNA + PA)(419)

- RF -Bewertungs- und Entwicklungskits, Boards(747)

- HF-gerichtete Kupplung(2718)

- RF Diplexer(1464)

- RF-Detektoren(412)

- RF-Demodulatoren(249)

- HF-Antennen(12319)

- HF-Verstärker(19651)

- Balun(1496)

- Dämpfungsglieder(4852)

-

Optoelektronik

Optoelektronik

- Optomechanisch(480)

- Leuchten(125)

- Laserdioden, Lasermodule - Laserlieferung, Laserfasern(345)

- Hene Lasersysteme(31)

- Hene Laserköpfe(27)

- Hintergrundbeleuchtung anzeigen(93)

- Xenon-Beleuchtung(387)

- Touchscreen-Overlays(453)

- Panel Indicators, Pilot Lights(75729)

- Optik-Remote-Phosphor-Lichtquelle(269)

- Optik-Reflektoren(665)

- Optik-leichte Rohre(5384)

- Optik-Objektive(4951)

- LEDs-Spacer, Unentschieden(2718)

- LEDs-Lamp-Ersetzungen(29718)

- LEDs - Leiterplattenindikatoren, Arrays, Lichtstäbe, Balkendiagramme(9083)

- LED-thermische Produkte(667)

- LED-Beleuchtung(64)

- LED-Beleuchtung-weiß(37580)

- LED-Beleuchtung-Farbe(4728)

- LED-Beleuchtung-Maiskolben, Motoren, Module(28735)

- LED-Anzeige-diskret(27601)

- Laserdioden, Module(1553)

- Lampen-Glühlampen, Neons(311004)

- Lampen-Kälte-Fluoreszenz (KKL) & UV(164)

- Wechselrichter(7728)

- Infrarot, UV, sichtbare Strahler(3871)

- Fiber Optics-Transmitter-Antrieb integriert(4085)

- Fiber Optics-Transmitter-diskrete(350)

- Fiber Optics-Transceiver Module(18758)

- Fiberoptik-Switches, Multiplexer, Demultiplexer(1387)

- Fiberoptik-Receiver(695)

- Fiberoptik-Dämpfung(654)

- Elektrolumineszenz(102)

- Display, Monitor-Interface Controller(98)

- Display-Module-Vakuum-Leuchtstofflampen (VFD)(249)

- Module anzeigen-LED Dot Matrix und Cluster(865)

- Display-Module-LED-Zeichen und numerische(5421)

- Display-Module-LCD, OLED, Graphic(4654)

- Display-Module-LCD, OLED-Zeichen und numerische(2202)

- Display-Blenden, Objektive(88)

- Adresse, Spezialität(458)

-

Sensoren, Wandler

Sensoren, Wandler

- Ultraschallempfänger, Sender - Industrial(115)

- Temperatursensoren - Thermostate - Mechanisch - Industrielles(3103)

- Temperatursensoren - Analog und digitaler Ausgang - Industrial(209)

- Näherungssensoren - Industrial(13611)

- Drucksensoren, Wandler - Industrie(26503)

- Optische Sensoren - Photonik - Zähler, Detektoren, SPCM (Einzelphotonzählmodul)(751)

- Optische Sensoren - Kameramodule(875)

- Magnetsensoren - Position, Nähe, Geschwindigkeit (Module) - Industrie(554)

- Kraftsensoren - Industrial(346)

- Flusssensoren - Industrielles(151)

- Float, Level Sensoren - Industrial(310)

- Encoder - Industrial(4980)

- Farbsensoren - Industrial(50)

- Berührungssensoren(100)

- Ultraschall-Receiver, Transmitter(2421)

- Temperatursensoren-Thermostat-Solid State(1096)

- Temperatursensoren-Thermostate-mechanisch(3397)

- Temperatursensoren - Thermoelemente, Temperatursonden(1921)

- Temperatursensoren - RTD (Widerstandstemperaturdetektor)(1525)

- Temperatursensoren-PTC-Thermistoren(2273)

- Temperatursensoren-ntc-thermistoren(13259)

- Temperatursensoren-Analog und Digital Output(3928)

- DMS(1399)

- Spezialisierte Sensoren(1861)

- Solarzellen(503)

- Schock-Sensoren(84)

- Sensor-Interface-Junction-Blöcke(2519)

- Sensor-Kabel-Baugruppen(22011)

- Proximity/Belegung Sensoren-fertige Einheiten(725)

- Näherungsschalter(2860)

- Drucksensoren, Wandler(11317)

- Positionssensoren - Winkel, lineare Positionsmessung(6022)

- Optische Sensoren-reflektierende-Logik-Ausgang(194)

- Optische Sensoren - reflektierend - analoge Ausgang(432)

- Optische Sensoren-Phototransistoren(1027)

- Optische Sensoren - Photointerrupter - Schlitztyp - Transistorausgang(1427)

- Optische Sensoren - Photointerrupter - Schlitztyp - Logikausgabe(1215)

- Optische Sensoren-Lichtschranke, Industrial(16763)

- Optische Sensoren-Photodioden(1543)

- Optische Sensoren-Foto-Detektoren-Remote Receiver(2605)

- Optische Sensoren-Foto-Detektoren-Logik-Ausgang(146)

- Optische Sensoren-Foto-Detektoren-CDs-Zellen(74)

- Optische Sensoren-Distanz-Messung(377)

- Optische Sensoren-Ambient Light, IR, UV Sensoren(1305)

- Multifunktions(558)

- Motion Sensors-Vibration(337)

- Motion Sensors-Tilt Schalter(67)

- Bewegungsmelder-optisch(719)

- Motion Sensors-Neigungssensoren(175)

- Motion Sensors-Imus (Trägheit-Maßeinheiten)(416)

- Motion Sensors-Kreisel(214)

- Motion Sensors-Beschleunigungsmesser(1911)

- Magnete-Sensor abgestimmt(119)

- Magnete-Multi Purpose(1965)

- Magnetische Sensoren-Schalter (Solid State)(3700)

- Magnetsensoren - Position, Nähe, Geschwindigkeit (Module)(5199)

- Magnetische Sensoren-linear, Kompass (ICS)(1247)

- Magnetsensoren - Kompass, Magnetfeld (Module)(35)

- LVDT -Wandler (linearer variabler Differentialtransformator)(204)

- IrDA Transceiver-Module(196)

- Bildsensor, Kamera(2235)

- Feuchtigkeit-Sensoren(1425)

- Gas-Sensoren(1217)

- Force Sensoren(188)

- Durchfluss-Sensoren(550)

- Float, Level Sensoren(1343)

- Encoder(6357)

- Staub-Sensoren(43)

- Aktuelle Wandler(3455)

- Color Sensoren(85)

- Verstärker(1905)

-

Anschlüsse, Verbindungen

Anschlüsse, Verbindungen

- USB, DVI, HDMI -Stecker(446)

- Festkörperbeleuchtungsstecker(555)

- Steckdosen für ICs, Transistoren(953)

- Steckbare Steckverbinder(1221)

- Photovoltaik (Solarpanel) Anschlüsse(136)

- Glasfaseranschlüsse(370)

- FFC, FPC (flache flexible) Anschlüsse(761)

- D-Sub, D-förmige Stecker(2887)

- Koaxialverbinder (RF)(2389)

- Rundanschlüsse(14162)

- Stromanbeter Blade Type(273)

- Stecker und Behälter(2597)

- USB, DVI, HDMI Stecker-Adapter(572)

- USB, DVI, HDMI -Stecker(4298)

- Klemmen-Wire to Board Steckverbinder(217)

- Klemmen-Draht-Steckverbinder(4322)

- Klemmen-Draht-Pin Stecker(328)

- Terminals-Revolver Steckverbinder(1273)

- Terminals-spezialisierte Steckverbinder(2042)

- Klemmen-Spaten Verbinder(3902)

- Klemmen-Löten/Stecker(345)

- Klemmen-Verschraubungen(745)

- Klemmen-Ring Steckverbinder(12596)

- Klemmen-rechteckige Steckverbinder(4747)

- Terminals - Schnellverbindungen, schnelle Trennungsanschlüsse(8514)

- Klemmen-PC PIN, Single Post Connectors(3776)

- Klemmen-PC-Pin-Buchsen, Sockel-Steckverbinder(5883)

- Klemmen-magnetische Draht-Steckverbinder(1653)

- Klemmen-Messer Steckverbinder(112)

- Klemmen-Gehäuse, Stiefel(2850)

- Klemmen-Folie Steckverbinder(108)

- Klemmen-Barrel, Bullet-Steckverbinder(1107)

- Klemmen-Adapter(137)

- Terminal-Streifen und Revolver-Boards(1159)

- Terminal Junction Systeme(2533)

- Anschlussblöcke-Draht an Bord(43615)

- Terminal Blocks-spezialisierte(3722)

- Terminal Blocks-Power Distribution(847)

- Anschlussblöcke-Panel Mount(1359)

- Terminal Blocks-Interface Module(1819)

- Anschlussblöcke-Kopfzeilen, Stecker und Buchsen(119920)

- Anschlussblöcke-DIN-Schiene, Kanal(9373)

- Anschlussblöcke-Kontakte(65)

- Anschlussblöcke-Barrier Blocks(47517)

- Anschlussblöcke-Adapter(1059)

- Solid State Lighting Verbinder-Kontakte(271)

- Festkörperbeleuchtungsstecker(1344)

- Buchsen für ICS, Transistoren-Adapter(275)

- Steckdosen für ICs, Transistoren(22148)

- Shunts, Jumper(907)

- Rechteckige Verbinder-Feder geladen(7721)

- Rechteckige Steckverbinder-Gehäuse(43023)

- Rechteckige Verbinder-Kopfzeilen, Spezial-PIN(6129)

- Rechteckige Anschlüsse - Header, Gefäße, weibliche Sockel(229601)

- Rechteckige Verbinder-Kopfzeilen, männliche Pins(543338)

- Rechteckige Anschlüsse - kostenloses Hängen, Panelhalterung(30142)

- Rechteckige Verbinder-Kontakte(10681)

- Rechteckige Anschlüsse - Board in, Direktdraht zum Board(2432)

- Rechteckige Verbinder-Adapter(475)

- Rechteckig - Brett zu Board -Steckern - Header, Behälter, weibliche Sockel(9)

- Rechteckig - Brett zu Board -Steckern - Header, männliche Stifte(2)

- Rechteckige Anschlüsse - Board -Abstandshalter, Stacker (Board zu Board)(238901)

- Rechteckige Anschlüsse - Arrays, Kantentyp, Mezzanin (Board zu Board)(37853)

- Stromanschluss-Eingänge, Steckdosen, Module(10310)

- Steckbare Steckverbinder(6049)

- Photovoltaik- (Solarpanel) Anschlüsse - Kontakte(77)

- Photovoltaik (Solarpanel) Anschlüsse(504)

- Modulare Steckverbinder-Verdrahtung Blöcke(99)

- Modulare Steckverbinder-Stecker(1674)

- Modulare Steckverbinder-Stecker Gehäuse(181)

- Modulare Steckverbinder-Buchsen mit magnetischen(10152)

- Modulare Steckverbinder-Buchsen(23416)

- Modulare Steckverbinder-Adapter(855)

- Memory Connectors-PC Cards-Adapter(21)

- Memory Connectors-PC Card Sockets(3299)

- Memory Connectors-Inline Modul Sockets(3390)

- LGH Steckverbinder(764)

- Keystone-Einsätze(2758)

- Keystone-Frontplatte, Frames(1926)

- Heavy Duty Steckverbinder-Einsätze, Module(4190)

- Schwerlastanschlüsse - Gehäuse, Kapuzen, Basen(17226)

- Heavy Duty Steckverbinder-Frames(523)

- Heavy Duty Steckverbinder-Kontakte(1832)

- Heavy Duty Steckverbinder-Baugruppen(671)

- LWL-Steckverbinder-Gehäuse(919)

- Glasfaser-Steckverbinder - Adapter(4455)

- LWL-Steckverbinder(3001)

- FFC, FPC (flache flexible) Steckverbinder - Gehäuse(652)

- FFC, FPC (flache flexible) Anschlüsse - Kontakte(202)

- FFC, FPC (flache flexible) Anschlüsse(18691)

- D-Sub, d-förmige Steckverbinder-Terminatoren(47)

- D-Sub, d-förmige Steckverbinder-Gehäuse(12238)

- D-Sub, d-förmige Steckverbinder-Kontakte(2714)

- D-Sub, D-förmige Steckverbinder-Rückenschalen, Kapuzen(5995)

- D-Sub, d-förmige Steckverbinder-Adapter(1304)

- D-Sub Steckverbinder(141346)

- D-förmige Steckverbinder-Centronics(8770)

- Kontakte, Frühling geladen und Druck(630)

- Kontakte-Multi Purpose(6196)

- Kontakte-"Leadframe"(122)

- Koaxial-Steckverbinder (RF)-Terminatoren(1231)

- Koaxial-Steckverbinder (RF)-Kontakte(480)

- Koaxial-Steckverbinder (RF)-Adapter(6386)

- Koaxialverbinder (RF)(25734)

- Rundsteckverbinder-Gehäuse(441226)

- Rundsteckverbinder-Kontakte(4737)

- Rundsteckverbinder-backschalen und Kabel-Klemmen(53692)

- Rundsteckverbinder-Adapter(8839)

- Rundanschlüsse(1196254)

- Card Edge Steckverbinder-Gehäuse(469)

- Karte Edge Verbinder-edgeboard Verbinder(672683)

- Card Edge Verbinder-Kontakte(325)

- Card Edge Verbinder-Adapter(73)

- Blade Type Power Steckverbinder-Gehäuse(837)

- Blade Type Power Connectors-Kontakte(393)

- Stromanbeter Blade Type(4163)

- Zwischen Serien-Adapter(649)

- Barrel-Stromanschluss(935)

- Barrel-Audio-Anschlüsse(2432)

- Barrel-Audio Adapter(92)

- Banana und Tip Steckverbinder-Buchsen, Stecker(1644)

- Banana and Tip Connectors-Binding Posts(239)

- Banana und Tip Steckverbinder-Adapter(75)

- Backplane Steckverbinder-spezialisiert(45586)

- Backplane Steckverbinder-Gehäuse(6863)

- Backplane Steckverbinder-Hard metrisch, Standard(6297)

- Backplane Steckverbinder-DIN 41612(9408)

- Backplane Steckverbinder-Kontakte(3583)

- Backplane Connectors-ARINC Einsätze(2357)

- Backplane Steckverbinder-ARINC(3789)

-

Widerstände

-

Kondensatoren

Kondensatoren

- Aluminium-Elektrolytkondensatoren(16817)

- Trimmer, Variable Kondensatoren(3151)

- Dünne Folien-Kondensatoren(3473)

- Tantal-Kondensatoren(136103)

- Tantal-Polymer-Kondensatoren(9778)

- Silizium-Kondensatoren(320)

- Niob Oxide Kondensatoren(330)

- Mica und PTFE Kondensatoren(9101)

- Folien-Kondensatoren(150406)

- Elektrische Doppelschichtkondensatoren (EDLC), Superkondensatoren(2782)

- Keramische Kondensatoren(833829)

- Kondensatoren-Netzwerke, Arrays(2383)

- Aluminium-Elektrolytkondensatoren(125325)

- Aluminium-Polymer-Kondensatoren(7544)

-

Transformatoren

-

Isolatoren

-

Kristalle, Oszillatoren, Resonatoren

-

Switches

Switches

- Verriegelungsschalter(2893)

- Emergency-Stop-Schalter (E-Stop)(1160)

- Kabelzugschalter(571)

- Toggle-Schalter(33608)

- Rändelrads Schalter(742)

- Schalter(14263)

- Snap-Aktion, Endschalter begrenzen(28077)

- Slide-Schalter(5166)

- Selector-Schalter(9720)

- Rotary Switches(13850)

- Rocker Schalter(53790)

- Drucktaste-Schalter-Hall-Effekt(127)

- Drucktaste Schalter(190826)

- Programmierbare Display-Switches(39)

- Navigations-Schalter, Joystick(1882)

- Magnetische, Reed-Schalter(1399)

- Keypad-Schalter(637)

- Keylock Schalter(3684)

- DIP Schalter(7747)

- Konfigurierbare Switch-Komponenten-Objektiv(1435)

- Konfigurierbare Schalter-Komponenten-Lichtquelle(1236)

- Konfigurierbare Switch-Komponenten-Contact Block(1401)

- Konfigurierbare Switch-Komponenten-Body(16077)

- Disconnect-Switch-Komponenten(2567)

-

Relais

Relais

- Sicherheitsrelais(1310)

- Reedrelais(1735)

- Hochfrequenz (RF) -Relais(1190)

- Schütze (Festkörper)(686)

- Schütze (elektromechanisch)(11952)

- Kfz-Relais(1881)

- Solid State Relais(10652)

- Signal-Relais, bis zu 2 Ampere(9149)

- Relay-Sockets(2075)

- Power Relays, über 2 Ampere(31604)

- E / A-Relaismodule(712)

- I/o-Relay-Module-Input(2)

- I/o-Relay-Modul-Racks(247)

Sprache auswählen

Aktuelle Sprache

Deutsch

- English

- Deutsch

- Italia

- Français

- 日本語

- 한국의

- русский

- Svenska

- Nederland

- español

- Português

- polski

- Suomi

- Gaeilge

- Slovenská

- Slovenija

- Čeština

- Melayu

- Magyarország

- Hrvatska

- Dansk

- românesc

- Indonesia

- Ελλάδα

- Български език

- Afrikaans

- IsiXhosa

- isiZulu

- lietuvių

- Maori

- Kongeriket

- Монголулс

- O'zbek

- Tiếng Việt

- हिंदी

- اردو

- Kurdî

- Català

- Bosna

- Euskera

- العربية

- فارسی

- Corsa

- Chicheŵa

- עִבְרִית

- Latviešu

- Hausa

- Беларусь

- አማርኛ

- Republika e Shqipërisë

- Eesti Vabariik

- íslenska

- မြန်မာ

- Македонски

- Lëtzebuergesch

- საქართველო

- Cambodia

- Pilipino

- Azərbaycan

- ພາສາລາວ

- বাংলা ভাষার

- پښتو

- malaɡasʲ

- Кыргыз тили

- Ayiti

- Қазақша

- Samoa

- සිංහල

- ภาษาไทย

- Україна

- Kiswahili

- Cрпски

- Galego

- नेपाली

- Sesotho

- Тоҷикӣ

- Türk dili

- ગુજરાતી

- ಕನ್ನಡkannaḍa

- मराठी

CD4027 Dual Package JK Flip-Flop IC Datenblatt und Spezifikationen

Zeit: 2026/03/19

Durchsuchen: 45

Katalog

Übersicht über CD4027

Die CD4027 Dual JK Flip-Flop IC ist ein CMOS-basierter digitaler integrierter Schaltkreis, der zwei unabhängige JK-Flip-Flops in einem einzigen Gehäuse enthält.Jedes Flip-Flop arbeitet mit einer Master-Slave-Konfiguration und ermöglicht so eine stabile und flankengesteuerte Datenspeicherung.Es umfasst Eingänge wie J, K, Clock, Set und Reset sowie komplementäre Ausgänge Q und Q̅.

Dieser IC ist für den Betrieb mit geringem Stromverbrauch ausgelegt und bietet eine hohe Störfestigkeit, wodurch er für digitale Logiksysteme zuverlässig ist.Es unterstützt einen breiten Betriebsspannungsbereich und gewährleistet eine konstante Leistung unter verschiedenen Schaltkreisbedingungen.Die asynchronen Set- und Reset-Eingänge ermöglichen eine direkte Steuerung des Ausgangs unabhängig vom Taktsignal.

Die JK-Logik bietet einen flexiblen Betrieb, einschließlich Halte-, Setz-, Reset- und Umschaltfunktionen, was den CD4027 zu einer vielseitigen Komponente für das sequentielle Logikdesign macht.

Wenn Sie am Kauf des CD4027 Dual JK Flip-Flop IC interessiert sind, kontaktieren Sie uns bitte bezüglich Preis und Verfügbarkeit.

CAD-Modelle von CD4027

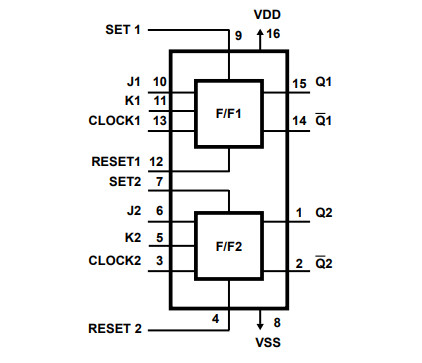

Pinbelegungsdetails von CD4027

|

Pin

Nein. |

Pin

Name |

Beschreibung |

|

1 |

Q2 |

Ausgabe von

Flip-Flop 2 |

|

2 |

Q̅2 |

Ergänzung

Ausgang von Flip-Flop 2 |

|

3 |

UHR 2 |

Clock-Eingang für

Flip-Flop 2 |

|

4 |

RESET 2 |

Asynchron

Reset für Flip-Flop 2 (aktiv HIGH) |

|

5 |

K2 |

K-Eingang für

Flip-Flop 2 |

|

6 |

J2 |

J-Eingang für

Flip-Flop 2 |

|

7 |

SET 2 |

Asynchroner Satz

für Flip-Flop 2 (aktiv HIGH) |

|

8 |

VSS |

Masse (0V) |

|

9 |

SET 1 |

Asynchroner Satz

für Flip-Flop 1 (aktiv HIGH) |

|

10 |

J1 |

J-Eingang für

Flip-Flop 1 |

|

11 |

K1 |

K-Eingang für

Flip-Flop 1 |

|

12 |

RESET 1 |

Asynchron

Reset für Flip-Flop 1 (aktiv HIGH) |

|

13 |

UHR 1 |

Clock-Eingang für

Flip-Flop 1 |

|

14 |

Q̅1 |

Ergänzung

Ausgang von Flip-Flop 1 |

|

15 |

Q1 |

Ausgabe von

Flip-Flop 1 |

|

16 |

VDD |

Positives Angebot

Spannung |

Alternativen und gleichwertiges Modell

• CD4027B

• 74HC76

• 74LS107

• 74LS109

• 74HC112

• CD4013B

Logikdiagramm von CD4027

Das Logikdiagramm des CD4027 zeigt eine Master-Slave-JK-Flip-Flop-Struktur, die stabile und kontrollierte Ausgangsänderungen gewährleistet.Die Schaltung ist in zwei Hauptabschnitte unterteilt: die Master-Stufe und die Slave-Stufe, die beide durch das Taktsignal gesteuert werden.Die Master-Stufe erfasst die Eingangsdaten (J und K), wenn der Takt auf LOW ist, während die Slave-Stufe den endgültigen Ausgang aktualisiert, wenn der Takt auf HIGH wechselt.Diese Anordnung verhindert unerwünschte Änderungen und gewährleistet einen flankengetriggerten Betrieb.

Die J- und K-Eingänge werden zunächst durch Logikgatter verarbeitet, die bestimmen, ob das Flip-Flop hält, setzt, zurücksetzt oder umschaltet.Diese Signale werden dann durch Transmission Gates (TG) geleitet, die als Schalter fungieren, die von der Uhr und ihrem Komplement gesteuert werden.Dadurch können Daten nur zum richtigen Zeitpunkt fließen, was die Zuverlässigkeit verbessert.

Die SET- und RESET-Eingänge sind asynchron, d. h. sie können den Ausgang unabhängig vom Takt direkt erzwingen.Die Ausgänge Q und Q̅ werden durch Inverterstufen erzeugt, wodurch komplementäre Signale gewährleistet werden.Darüber hinaus enthält das Diagramm CMOS-Schutznetzwerke, um die Eingänge vor Spannungsspitzen zu schützen.

Funktionsblockdiagramm

Spezifikationen von CD4027

|

Parameter |

Wert |

|

Typ |

JK Flip-Flop |

|

Anzahl

Kanäle |

2 |

|

Anzahl der Pins |

16 |

|

Paket/Koffer |

16-SOIC

(0,154", 3,90 mm Breite) |

|

Montageart |

Oberflächenmontage |

|

Terminalformular |

Möwenflügel |

|

Ausgabetyp |

Differenzial |

|

Polarität |

Nicht invertierend |

|

Triggertyp |

Positive Kante |

|

Taktfrequenz |

Bis zu 24 MHz |

|

Maximale Frequenz

(Nom)

|

3,5 MHz |

|

Vermehrung

Verzögerung |

300 ns |

|

Maximale Ausbreitung

Verzögerung |

90 ns bei 15 V,

50pF |

|

Einschaltverzögerung

Zeit |

45 ns |

|

Versorgungsspannung

Reichweite |

3V – 18V |

|

Typisches Angebot

Spannung |

5V |

|

Versorgungsspannung

(Min.) |

3V |

|

Ausgangsstrom |

6,8mA |

|

Stromversorgung

Strom (Max) |

0,06mA |

|

Ruhend

Strom (Iq) |

4 µA |

|

Ladekapazität |

50 pF |

|

Eingabe

Kapazität |

5 pF |

|

Betrieb

Temperatur |

-55°C bis +125°C |

|

Spitzen-Reflow

Temperatur |

260°C |

|

Feuchtigkeit

Empfindlichkeitsstufe |

MSL 1

(Unbegrenzt) |

|

Kontaktbeschichtung |

Gold |

|

Verpackung |

Rohr |

|

Serie |

4000B |

|

Basisteilenummer |

CD4027 |

|

Logikfunktion |

UND, JK

Flip-Flop |

|

Anzahl der Bits

pro Element |

1 |

|

Terminal

Position |

Dual |

|

ECCN-Code |

EAR99 |

|

Pb-freier Code |

Ja |

|

RoHS-Status |

RoHS3-konform |

|

Bleifrei |

Ja |

|

Strahlung

Härten |

Nein |

|

Höhe |

1,75 mm |

|

Breite |

3,91 mm |

|

Länge |

9,9 mm |

|

Dicke |

1,58 mm |

|

Gewicht |

141,69 mg |

|

Lebenszyklusstatus |

Aktiv |

Merkmale von CD4027

Hochspannungsbetrieb (20 V Nennleistung)

Der CD4027 unterstützt den Hochspannungsbetrieb bis zu 20 V und ist somit für eine Vielzahl von CMOS-Logikschaltungen geeignet.Diese Flexibilität ermöglicht eine stabile Leistung über verschiedene Versorgungsbedingungen hinweg.

Fähigkeit zum Festlegen und Zurücksetzen

Es verfügt über asynchrone Set- und Reset-Eingänge, die eine direkte Steuerung des Ausgangszustands ermöglichen.Dies gewährleistet eine schnelle Initialisierung oder erzwungene Ausgangsänderungen unabhängig vom Taktsignal.

Statischer Flip-Flop-Betrieb

Der IC behält seinen logischen Zustand auf unbestimmte Zeit bei, solange Strom zugeführt wird.Es sind keine kontinuierlichen Taktimpulse erforderlich, was die Zuverlässigkeit speicherbasierter Schaltkreise verbessert.

Betrieb mit mittlerer Geschwindigkeit

Der CD4027 bietet eine typische Taktwechselrate von etwa 16 MHz bei 10 V.Dies sorgt für ein Gleichgewicht zwischen Geschwindigkeit und geringem Stromverbrauch für digitale Designs.

Symmetrische Ausgabeeigenschaften

Es liefert ausgewogene Anstiegs- und Abfallzeiten an den Ausgängen.Dies trägt zur Aufrechterhaltung einer konsistenten Signalintegrität bei und verbessert die Gesamtleistung der Schaltung.

Niedriger Eingangsstrom

Der IC verfügt über einen sehr niedrigen Eingangsstrom (nur 1 µA bei 18 V), was den Stromverbrauch reduziert und ihn für energieeffiziente Designs geeignet macht.

Großer Rauschabstand

Der CD4027 bietet eine hohe Störfestigkeit über verschiedene Versorgungsspannungen hinweg.Dies gewährleistet einen stabilen Betrieb auch in elektrisch verrauschten Umgebungen.

Standardisierte CMOS-Leistung

Es erfüllt die JEDEC-Standards für CMOS-Geräte der 4000B-Serie und gewährleistet so Kompatibilität, Zuverlässigkeit und konsistente elektrische Eigenschaften über alle Anwendungen hinweg.

CD4027 Arbeiten im Schaltkreis

Die Schaltung zeigt, wie das Dual-JK-Flip-Flop CD4027 als Steuerelement in einem Schaltsystem verwendet wird.Auf der linken Seite erkennt ein TSOP1738-Infrarotempfänger eingehende IR-Signale und wandelt sie in elektrische Impulse um.Diese Impulse werden durch passive Komponenten wie Widerstände und Kondensatoren konditioniert, die dabei helfen, Rauschen zu filtern und das Signal zu stabilisieren, bevor es an die CD4027-Eingänge gesendet wird.

Innerhalb der Schaltung verarbeitet der CD4027 das eingehende Signal und schaltet seinen Ausgangszustand basierend auf dem Takteingang um.Dieses Verhalten ermöglicht es dem Flip-Flop, als Speicherelement zu fungieren und seinen Zustand jedes Mal zu ändern, wenn ein gültiges Signal empfangen wird.Durch den Einsatz unterstützender Komponenten wird ein korrektes Timing und eine zuverlässige Auslösung des Flip-Flops gewährleistet.

Ausgangsseitig verstärkt eine Transistortreiberstufe (2N4403) das Signal vom IC.Dadurch werden ein Relais und eine Anzeige-LED angesteuert, wodurch eine externe Last gesteuert werden kann.Über der Relaisspule befindet sich eine Diode, um den Stromkreis beim Schalten vor Spannungsspitzen zu schützen.

Anwendungen von CD4027

• Binärzähler

• Frequenzteiler

• Kippschalter

• Schieberegister

• Datenspeicherschaltungen

• Digitaluhren

• Steuerkreise

• Zeitschaltkreise

• Impulserzeugungsschaltungen

• Sequenzgeneratoren

Vergleich: CD4027 vs. CD4013

|

Parameter |

CD4027 |

CD4013 |

|

Flip-Flop-Typ |

JK Flip-Flop |

D Flip-Flop |

|

Anzahl

Flip-Flops |

Dual (2) |

Dual (2) |

|

Eingabetyp |

J-, K-Eingänge |

D (Daten)-Eingang |

|

Betrieb |

Umschalten, Einstellen,

Zurücksetzen, Halten |

Datenlatch

(speichert Eingabewert) |

|

Komplexität |

Flexibler

(JK-Logik) |

Einfacher (einzeln

Dateneingabe) |

|

Taktauslöser |

Positiv

flankengesteuert |

Positiv

flankengesteuert |

|

Asynchron

Eingaben |

Einstellen und Zurücksetzen |

Einstellen und Zurücksetzen |

|

Ausgabe |

Q und Q̅ |

Q und Q̅ |

|

Logikfunktion |

Vielseitig (kann

als SR, T oder D fungieren) |

Fester D-Typ

Verhalten |

|

Design-Nutzung |

Komplexe Logik

Design |

Einfache Daten

Lagerung |

|

Macht

Verbrauch |

Niedrig (CMOS) |

Niedrig (CMOS) |

|

Versorgungsspannung

Reichweite |

3V – 18V |

3V – 18V |

|

Pakettyp |

16-polig |

14/16-polig |

|

Geschwindigkeit |

Mäßig |

Mäßig |

Abmessungen und Pad-Layout von CD4027

Fazit

Der CD4027 Dual JK Flip-Flop IC ist eine zuverlässige Lösung für das sequentielle Logikdesign.Aufgrund seiner Fähigkeit, mehrere Logikfunktionen auszuführen, kombiniert mit einem stabilen Master-Slave-Betrieb und einer hohen Störfestigkeit, eignet es sich für eine Vielzahl digitaler Systeme.Das detaillierte Verständnis der Pinbelegung, der internen Logik, der Spezifikationen und des Arbeitsverhaltens hilft Ihnen, effizientere und zuverlässigere Schaltkreise zu entwerfen.Durch den Vergleich mit ähnlichen ICs und die Erkundung der Alternativen können Sie die für Ihre spezifischen Anforderungen am besten geeignete Komponente auswählen.

Häufig gestellte Fragen [FAQ]

1. Was ist der Unterschied zwischen Master-Slave- und flankengetriggerten Flip-Flops?

Master-Slave-Flip-Flops verwenden zwei Stufen, um Race Conditions zu verhindern, während flankengetriggerte Flip-Flops für ein präzises Timing nur bei Taktübergängen aktualisiert werden.

2. Wie beseitigt ein JK-Flip-Flop den ungültigen Zustand von SR-Flip-Flops?

Es verwendet eine Rückkopplungslogik, sodass der Ausgang umschaltet, anstatt instabil zu werden, wenn beide Eingänge HIGH sind.

3. Kann der CD4027 ohne Taktsignal betrieben werden?

Ja, aber nur die asynchronen Set- und Reset-Eingänge steuern den Ausgang ohne Taktbeteiligung.

4. Was passiert, wenn SET und RESET gleichzeitig aktiviert werden?

Dies kann zu einem undefinierten Ausgangszustand führen, daher sollte dieser Zustand beim Schaltungsentwurf vermieden werden.

5. Wie wandelt man mit CD4027 ein JK-Flip-Flop in ein T-Flip-Flop um?

Verbinden Sie die Eingänge J und K miteinander.Der Ausgang schaltet bei jedem Taktimpuls um.

6. Ist CD4027 mit TTL-Logikschaltungen kompatibel?

Nicht direkt;Möglicherweise ist eine Pegelverschiebung erforderlich, da es sich um ein CMOS-Gerät mit unterschiedlichen Spannungspegeln handelt.

7. Welche Rolle spielen Transmission Gates im CD4027?

Sie steuern den Signalfluss zwischen den Stufen basierend auf dem Takt und sorgen so für richtiges Timing und Isolierung.

8. Wie reduzieren Sie Rauschprobleme beim Einsatz von CD4027 in Schaltkreisen?

Verwenden Sie geeignete Entkopplungskondensatoren, kurze Leitungen und stabile Stromversorgungsanschlüsse.

9. Was ist der Unterschied zwischen Q- und Q̅-Ausgängen?

Q̅ ist die Umkehrung von Q und liefert komplementäre Signale für logische Operationen.

10. Wie kann der ordnungsgemäße Betrieb des CD4027 getestet werden?

Legen Sie Taktimpulse an und variieren Sie die J- und K-Eingänge, während Sie die Q- und Q̅-Ausgänge überwachen, um das erwartete Verhalten zu überprüfen.

Verwandter Artikel

Verwandte -Produkte

C3216C0G2J152J115AA

CAP CER 1500PF 630V C0G 1206

12105C224MAT2A

CAP CER 0.22UF 50V X7R 1210

XC3S700A-4FG484C

IC FPGA 372 I/O 484FBGA

PIC16F627-20/SO

IC MCU 8BIT 1.75KB FLASH 18SOIC

KSZ8041FTL

IC TRANSCEIVER FULL 1/1 48TQFP

RMCF0402FT3K60

RES 3.6K OHM 1% 1/16W 0402

TLV2452CDGKR

IC OPAMP GP 2 CIRCUIT 8VSSOP

IDT71216S9PF

IDT71216S9PF IDT

LM10520MHX

LM10520MHX NS

LT1643HCGN

LT1643HCGN LINEAR

CY244ZXC-01C

CY244ZXC-01C CYPRESS-P

TC4094BF

TC4094BF TOSHIBA

AM29LV160BB-90WCI

AM29LV160BB-90WCI AMD